## Low-cost countermeasures against physical attacks on cryptographic algorithms implemented on altera FPGAs

Maxime Nassar

#### ► To cite this version:

Maxime Nassar. Low-cost countermeasures against physical attacks on cryptographic algorithms implemented on altera FPGAs. Other. Télécom ParisTech, 2012. English. NNT: 2012ENST0010 . pastel-00790669

#### HAL Id: pastel-00790669 https://pastel.hal.science/pastel-00790669

Submitted on 20 Feb 2013  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **Doctorat ParisTech**

#### THÈSE

pour obtenir le grade de docteur délivré par

#### **TELECOM** ParisTech

#### Spécialité « Électronique et Communication »

présentée et soutenue publiquement par

Maxime NASSAR

le 09 Septembre 2012

#### Contre-mesures à bas coût contre les attaques physiques sur

#### algorithms cryptographics implémentés sur FPGA Altera

Directeurs de thèse : Jean-Luc DANGER et René MARTIN Co-encadrement de la thèse : Sylvain GUILLEY

Jury Mme Elisabeth OSWALD, University of Bristol, UK M. Lionel TORRES, LIRMM, France M. Jens-Peter KAPS, George Mason University, USA M. Victor LOMNÉ, ANSSI, France M. Habib MEHREZ, LIP6, France

Rapporteur Rapporteur Examinateur Examinateur Président du jury T H È S E

TELECOM ParisTech

école de l'Institut Télécom - membre de ParisTech

To Laure and Nabil.

#### Acknowledgements

This PhD was performed in association between the *Trustway* group of Bull and *SEN* (Systemes Electronique Numérique) group of Department COM-ELEC (Communications & Electronique) of Telecom-ParisTech. These three years gave me the rare opportunity to both learn the essence of research and understand the ways of industrial engineering. This was made possible by meeting and interacting with those two groups of very smart, experienced and friendly people.

First and foremost, I would like to deeply thank my two PhD directors, Professor Jean-Luc Danger of Telecom-ParisTech and René Martin of Bull for trusting and guiding me through this three years. I also extend my sincere thankfulness to Dr. Sylvain Guilley and Patrick Le-Quéré for their numerous teachings and advices in both research and technical fields. It has been my great pleasure to work and interact with those gentlemen who are all specialists in their domains, but more importantly have great human skills.

Furthermore, I am extremely grateful to all the members of my jury who took the time to thoroughly analyse my work. I had the chance to be approved and perform my PhD defense before such renowned specialists for which I feel deeply honoured.

Finally I was fortunate to have the constant support and encouragement of my friends and family without which none of this would have been possible.

#### Abstract

Side-Channel Analysis (SCA) and Fault Attacks (FA) are techniques to recover sensitive information concealed in cryptographic embedded systems by exploiting unintentional physical leakage, such as the power consumption or the radiated magnetic field. As such attacks are low-cost and easily set–up in practice, they prove to be a serious threat to most sensitive devices. Therefore, when a high level of security is required, specific countermeasures must be manually deployed by the designer, as such functionality are generally not available in current CAD software tools.

FPGA technology is often chosen for low and middle volume applications even for high-end embedded systems where high performances and flexibility are mandatory as well as state of the art security. However, it has been put to light that such devices show great intrinsic vulnerabilities against SCAs and should therefore be protected with adequate countermeasures, able to compensate for those weaknesses.

This thesis has two main goals. On one hand, a review of the state of the art of FPGA-compatible countermeasure against SCA for both symmetrical and asymmetrical ciphering, in order to compare them in terms of performances, area and security level. In the event where none fit the required specifications, alternate countermeasures should be designed. On the other hand, the implementation of the selected protections for standard or customized algorithms with the minimum area overhead, either with automatised design flows or as a hand-made Intellectual Properties (IPs).

Symmetrical algorithms, specially AES, are first studied and several vulnerabilities of usual protections, namely Dual-rail with Precharge Logic (DPL) and masking are analysed, as well as the issue of performance and area overheads. In this context, three new countermeasures are considered:

- 1. Balance placement and routing (PAR) strategies aiming at enhancing existing DPLs robustness when implemented in modern FPGAs.

- 2. A new type of DPL called Balanced Cell-based Dual-rail Logic (BCDL), based on the use of a global precharge signal and synchronisation schemes to thwart most of the known DPL weaknesses. BCDL also possess a built-in fault resilience mechanism for simple stuck-at faults and provides implementation optimisations, achieving competitive performances and area overhead.

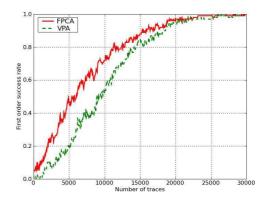

- 3. The Rotating S-Box Masking (RSM), a new masking technique for the AES. On the one hand, the frequency output and robustness level of RSM against firstorder SCAs are equivalent to a state of the art masking scheme. On the other hand, it brings a significant reduction of the area overhead, as well as robustness to other SCAs like the Variance Power Analysis (VPA), known to be efficient against usual masking. Like most masking schemes, RSM is however not naturally protected against fault attacks, implying that a classical fault detection

technique, for instance a deciphering and comparison, should be additionally implemented.

Regarding asymmetrical algorithms, current countermeasures already offer a robustness level and implementation cost suitable for industrial applications, against both passive and fault attacks. Therefore, rather than devising new mechanisms, a simple Elliptic Curve Cryptography (ECC) core is implemented on FPGA and SCAs are performed to verify the theoretical security level of the chosen protections.

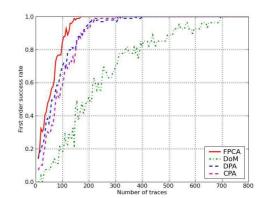

Finally, as designing an efficient countermeasure generally requires a fine understanding of the attack process and as classical SCA may not be sufficient to properly evaluate the robustness of every countermeasure, several new SCAs are presented and evaluated. Firstly the "Rank Corrector" (RC), rather than an actual SCA, is a SCA enhancement algorithm, designed to reduce the number of observations required to perform a successful attack. RC can be used to complement most existing SCAs like Differential Power Analysis (DPA) and Correlation Power Analysis (CPA). Secondly, The First Principal Components Analysis (FPCA), introduces a novel SCA distinguisher based on the Principal Component Analysis (PCA). FPCA proves to be more efficient than classical DPA or CPA on an unprotected DES implementation and VPA on a masked DES architecture. Then, combinations of either acquisition methods or SCA distinguishers are discussed and show significant decrease in the number of measurements required to perform a successful attack.

# Contents

| Ał | Abstract v         |          |                                       |    |  |

|----|--------------------|----------|---------------------------------------|----|--|

| Li | List of Figures xi |          |                                       |    |  |

| Li | st of A            | Algorit  | hms xi                                | ii |  |

| Gl | lossar             | y        | x                                     | v  |  |

| 1  | Intro              | oductio  | n                                     | 1  |  |

|    | 1.1                | Contex   | xt                                    | 1  |  |

|    | 1.2                | Organ    | ization                               | 1  |  |

| 2  | Phys               | sical Cr | yptanalysis on FPGA, State of the art | 3  |  |

|    | 2.1                | Gener    | ic SCAs                               | 3  |  |

|    |                    | 2.1.1    | Simple Analyses                       | 4  |  |

|    |                    | 2.1.2    | Timing Attack                         | 6  |  |

|    |                    | 2.1.3    | Statistical SCAs                      | 7  |  |

|    |                    | 2.1.4    | Profiling Attacks                     | 9  |  |

|    | 2.2                | Specifi  | ic SCAs on Asymmetrical Algorithms    | 0  |  |

|    |                    | 2.2.1    | Doubling attack                       | 0  |  |

|    |                    | 2.2.2    | Comparative Power Analysis            | 1  |  |

|    |                    | 2.2.3    | Address-bit DPA 1                     | 2  |  |

|    |                    | 2.2.4    | Carry-Leakage based Attack 1          | 2  |  |

|    |                    | 2.2.5    | RPA and ZPA   1                       | 13 |  |

|    | 2.3                | Gener    | ic Fault Attacks                      | 4  |  |

|    |                    | 2.3.1    | Differential Fault Attack             | 4  |  |

|    |                    | 2.3.2    | Safe Error Attack                     | 15 |  |

|    | 2.4                | Specifi  | ic Fault Attacks on ECC               | 15 |  |

|    |                    | 2.4.1    | Invalid Point Attacks                 | 15 |  |

|    |                    | 2.4.2    | Invalid Curve Attacks                 | 6  |  |

|    |                    | 2.4.3    | Twist Curve Attack   1                | l6 |  |

#### CONTENTS

| 3 | FPG | GA Countermeasures, State of the art                      |                    | 17        |

|---|-----|-----------------------------------------------------------|--------------------|-----------|

|   | 3.1 | Generic Countermeasures                                   |                    | 17        |

|   | 3.2 | 2 Countermeasures Against Passive Attacks on Symmetr      | rical Algorithms . | 18        |

|   |     | 3.2.1 Masking                                             |                    | 18        |

|   |     | 3.2.2 DPLs                                                |                    | 23        |

|   | 3.3 | 3 Countermeasures Against Passive Attacks on Asymme       | trical Algorithms  | 30        |

|   |     | 3.3.1 Against Simple Analyses                             |                    | 30        |

|   |     | 3.3.2 Against Statistical Attacks                         |                    | 35        |

|   |     | 3.3.3 ECC Specific Countermeasures                        |                    | 40        |

|   | 3.4 | U                                                         |                    | 43        |

|   |     | 3.4.1 Generic Countermeasures                             |                    | 43        |

|   |     | 3.4.2 Specific Schemes for Asymmetrical Algorithms        |                    | 44        |

| 4 | New | ew DPL Countermeasures for Symmetrical Algorithms         |                    | 47        |

|   | 4.1 | DPL Vulnerabilities                                       |                    | 47        |

|   |     | 4.1.1 Early Propagation Effect                            |                    | 47        |

|   |     | 4.1.2 Technological Bias                                  |                    | 49        |

|   |     | 4.1.3 Successful Attack on DES WDDL                       |                    | 51        |

|   |     | 4.1.4 Counteracting DPL vulnerabilities                   |                    | 57        |

|   | 4.2 | 2 Optimized Placing and Routing for DPL Countermeasu      | ures               | 58        |

|   |     | 4.2.1 Balanced Placement on Altera Stratix                |                    | 59        |

|   |     | 4.2.2 Placement-induced Routing with <i>LogicLocks</i> on |                    |           |

|   |     | GAs                                                       |                    | 63        |

|   | 4.3 | 0                                                         |                    | 71        |

|   |     | 4.3.1 BCDL Principle                                      |                    | 71        |

|   |     | 4.3.2 Implementation on Stratix II                        |                    | 78        |

|   |     | 4.3.3 Experimental Results                                |                    | 81        |

|   | 4.4 | Comparative DPL Overview and Conclusion                   |                    | 87        |

| 5 | New | ew Masking Scheme for AES                                 |                    | <b>91</b> |

|   | 5.1 | 0 5                                                       |                    | 91        |

|   | 5.2 | 0 0 ,                                                     |                    | 95        |

|   |     | 5.2.1 RSM: Principle and Implementation                   |                    |           |

|   |     | 5.2.2 Practical Robustness Evaluation                     |                    |           |

|   | 5.3 | 5                                                         |                    |           |

|   |     | 5.3.1 Information Theoretic Evaluation of the Counter     |                    |           |

|   |     | 5.3.2 Security against CPA and 2O-CPA                     |                    |           |

|   |     | 5.3.3 Exploring More Solutions Using SAT-Solvers .        |                    |           |

|   | 5.4 | 1                                                         |                    |           |

|   |     | 5.4.1 Surface-security trade-off                          |                    |           |

|   |     | 5.4.2 Time-security trade-off                             |                    |           |

|   |     | 5.4.3 Using partial reconfiguration                       |                    |           |

|   | 5.5 | 5 Conclusion                                              | •••••              | 117       |

| 6 | Exp | erimen   | tal Evaluation of Countermeasures for Asymmetrical Algorithms 119   |

|---|-----|----------|---------------------------------------------------------------------|

|   | 6.1 | Simpl    | e ECC design                                                        |

|   |     | 6.1.1    | Point doubling                                                      |

|   |     | 6.1.2    | Point addition                                                      |

|   |     | 6.1.3    | Modular operators                                                   |

|   |     | 6.1.4    | Unprotected Datapath                                                |

|   |     | 6.1.5    | Double an Add Always Implementation                                 |

|   |     | 6.1.6    | Protected implementation with "Random Splitting of Scalar" 125      |

|   | 6.2 | Exper    | imental Results                                                     |

|   |     | 6.2.1    | SPA on the Unprotected Implementation                               |

|   |     | 6.2.2    | SPA on the Double an Add Always                                     |

|   |     | 6.2.3    | "Doubling Attack" on the Double an Add Always                       |

|   |     | 6.2.4    | "Doubling Attack" on the Random Splitting of Scalar 130             |

|   | 6.3 | Concl    | usion                                                               |

| 7 | Des | ign of I | New Attacks 133                                                     |

|   | 7.1 | 0        | Principal Component Analysis (FPCA)                                 |

|   |     | 7.1.1    | FPCA: Principle                                                     |

|   |     | 7.1.2    | Reference Statistic                                                 |

|   |     | 7.1.3    | FPCA distinguisher                                                  |

|   |     | 7.1.4    | FPCA vs DES and masked DES                                          |

|   | 7.2 | Comb     | vined Attacks: Measurements Combination                             |

|   |     | 7.2.1    | Theoretical Background                                              |

|   |     | 7.2.2    | Experimental Results                                                |

|   | 7.3 | Comb     | pined Attacks: Distinguisher Combination                            |

|   |     | 7.3.1    | Mathematical Background                                             |

|   |     | 7.3.2    | Gini Correlation: A Mixture of Pearson and Spearman Coefficients144 |

|   |     | 7.3.3    | Pearson-Spearman Combination: An Empirical Approach 146             |

|   |     | 7.3.4    | Experimental Results and Discussion                                 |

|   | 7.4 | Rank     | Corrector                                                           |

|   |     | 7.4.1    | Background                                                          |

|   |     | 7.4.2    | Application field                                                   |

|   |     | 7.4.3    | Basic Principle                                                     |

|   |     | 7.4.4    | RC Parameters and their evaluation                                  |

|   |     | 7.4.5    | Description of the algorithm                                        |

|   |     | 7.4.6    | Example                                                             |

|   |     | 7.4.7    | Optimization                                                        |

|   |     | 7.4.8    | Experimental Results                                                |

|   | 7.5 | Concl    | usion                                                               |

| 8 | Con | clusio   | n and Perspectives 161                                              |

|   | 8.1 |          | uding Remarks                                                       |

|   | 8.2 | Persp    | ectives                                                             |

|   |     |          |                                                                     |

| List of Publications | <b>162</b> |

|----------------------|------------|

| Bibliography         | 165        |

# **List of Figures**

| 2.1  | SPA on DES                                                                   | 5  |

|------|------------------------------------------------------------------------------|----|

| 2.2  | SPA on RSA.                                                                  | 6  |

| 2.3  | Statistical SCA global framework                                             | 8  |

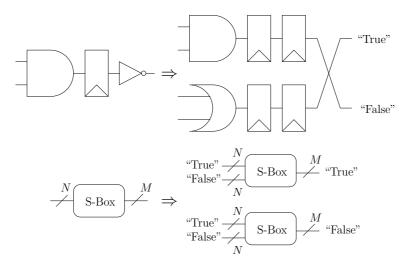

| 3.1  | 0                                                                            | 23 |

| 3.2  | 0                                                                            | 24 |

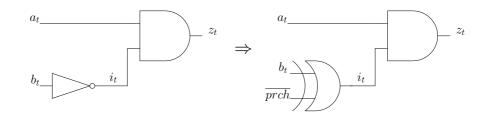

| 3.3  | From WDDL to WDDL with Divided Back-end Duplication                          | 25 |

| 3.4  | SDDL XOR Gate                                                                | 26 |

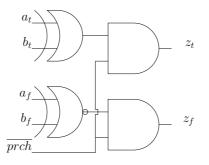

| 3.5  | (a) MDPL AND. (b) MDPL DFF                                                   | 28 |

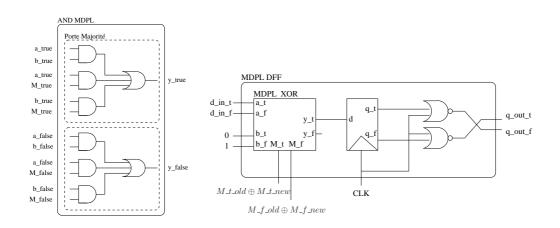

| 3.6  | 0 1                                                                          | 29 |

| 3.7  | (a) STTL Gate Example . (b) STTL AND                                         | 30 |

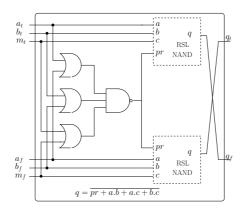

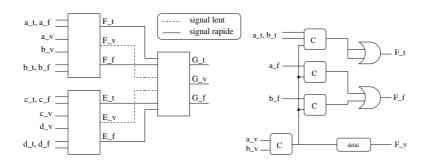

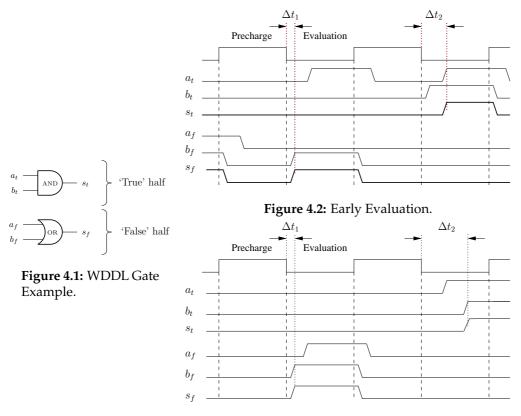

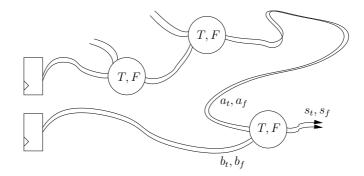

| 4.1  | WDDL Gate Example.                                                           | 48 |

| 4.2  | Early Evaluation.                                                            | 48 |

| 4.3  | Early Evaluation Combined With Imbalance of Dual Nets.                       | 48 |

| 4.4  | Unbalance in logical paths.                                                  | 49 |

| 4.5  | Unconstrained DES S-Box # 5 in Stratix                                       | 52 |

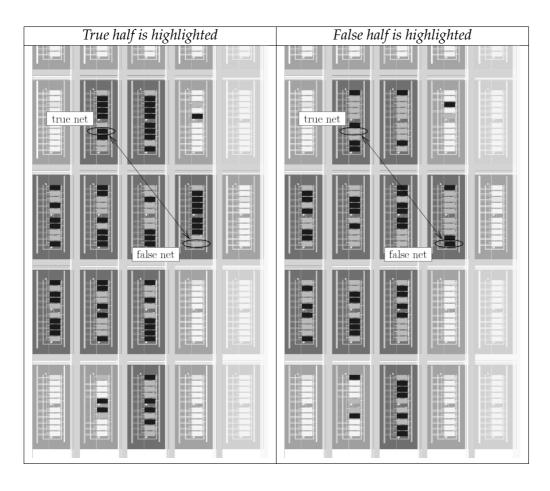

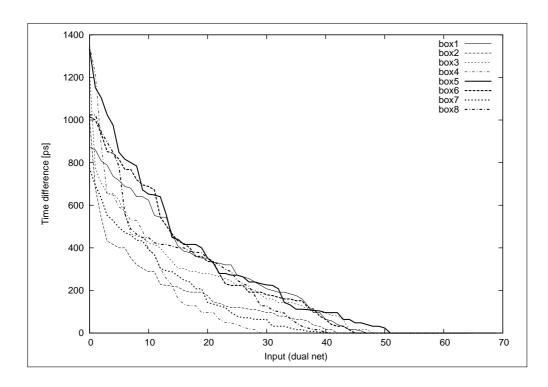

| 4.6  | $\Delta t$ decrease for the eight DES S-Boxes                                | 54 |

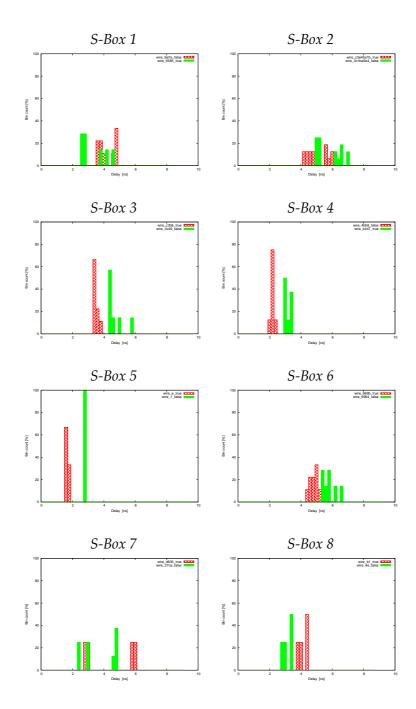

| 4.7  | Switching delay of the most vulnerable nodes (true and false nets)           | 55 |

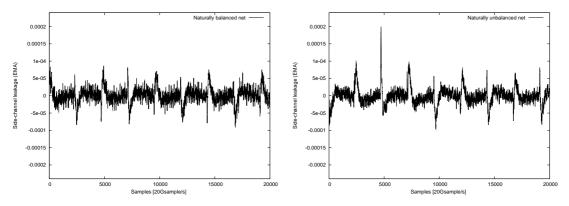

| 4.8  | Experimental covariance between the power traces and a regular net           |    |

|      | (left – no leakage) & the most critical net value (right – peak around       |    |

|      | sample 5,000)                                                                | 56 |

| 4.9  | Possible glitch in DRSL due to lack of synchronization before the precharge. | 59 |

| 4.10 | Constrained dual-placed DES S-Box # 5 in a Stratix (zoom on two adja-        |    |

|      | cent LABs).                                                                  | 61 |

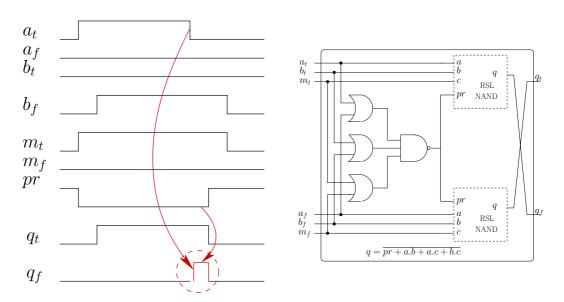

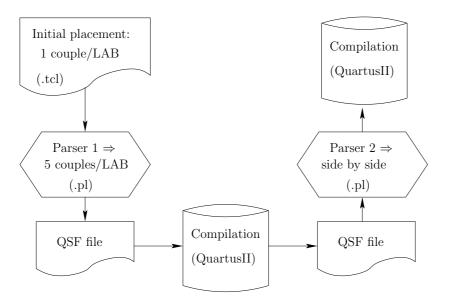

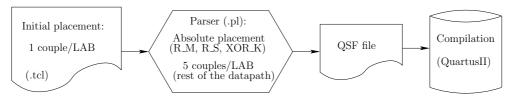

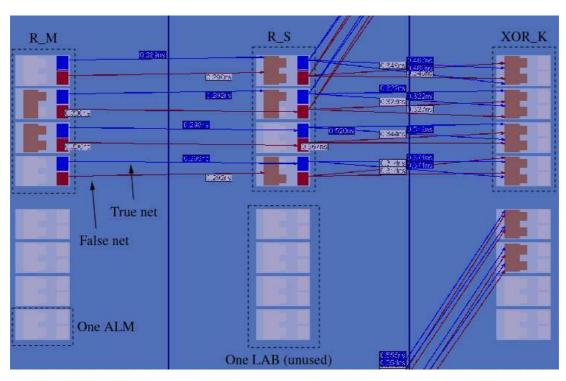

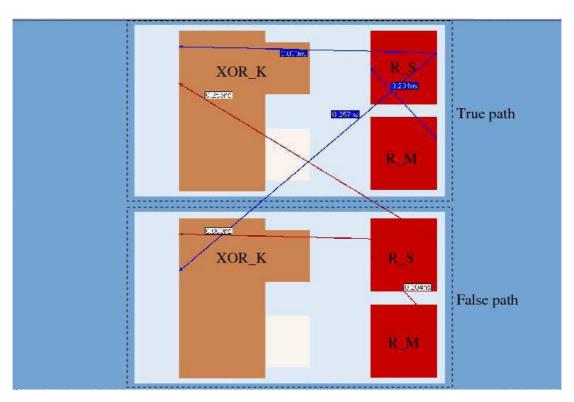

|      | Design Flow with Balanced placement on Stratix.                              | 62 |

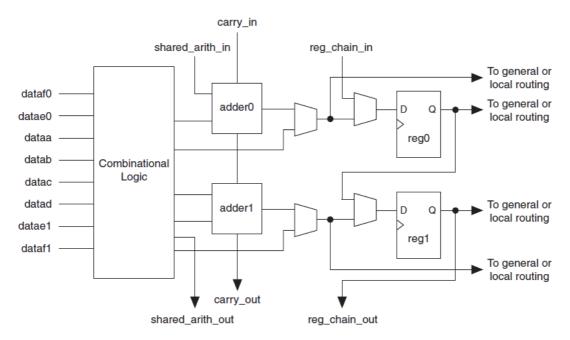

| 4.12 | High-Level block diagram of an ALM, extracted from "Stratix II Device        |    |

|      |                                                                              | 64 |

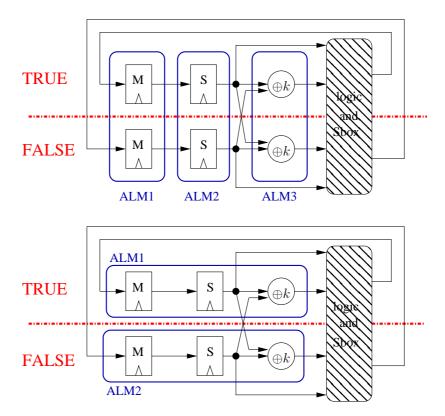

|      | 0                                                                            | 65 |

|      | 0                                                                            | 66 |

|      | 85                                                                           | 68 |

| 4.16 | Horizontal strategy.                                                         | 69 |

#### LIST OF FIGURES

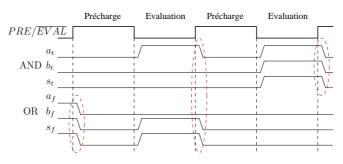

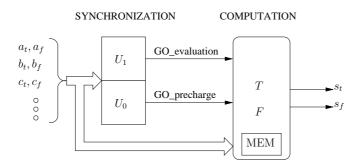

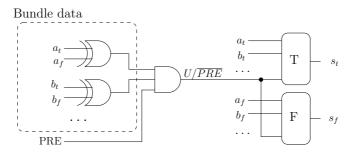

| 4.17 | Synchronization and "bundled" data in BCDL                                                                 | 72    |

|------|------------------------------------------------------------------------------------------------------------|-------|

| 4.18 | BCDL <i>n</i> -input cell.                                                                                 | 73    |

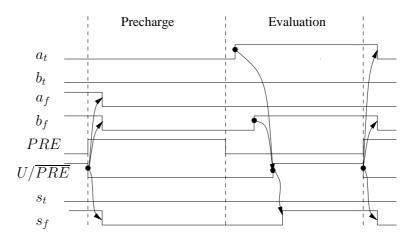

| 4.19 | Temporal relationships of a 2-input BCDL OR gate signals                                                   | 73    |

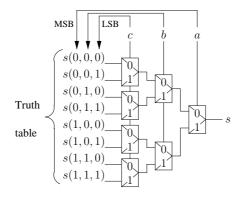

| 4.20 | Structure of a LUT.                                                                                        | 74    |

| 4.21 | Local switching balance in BCDL: LUT3 example                                                              | 75    |

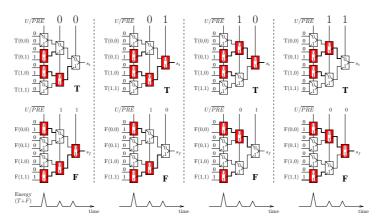

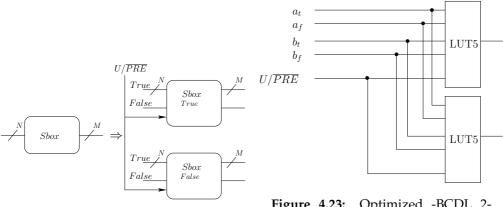

| 4.22 | BCDL S-Boxes                                                                                               | 76    |

| 4.23 | Optimized -BCDL 2-input gate                                                                               | 76    |

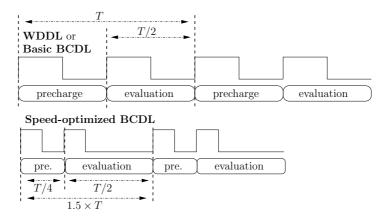

| 4.24 | Basic BCDL versus speed-optimized BCDL timings.                                                            | 77    |

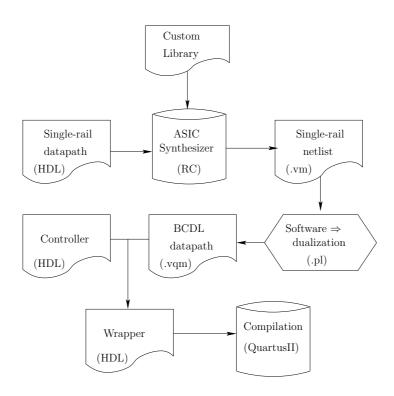

| 4.25 | BCDL Top-Down Compilation Flow.                                                                            | 79    |

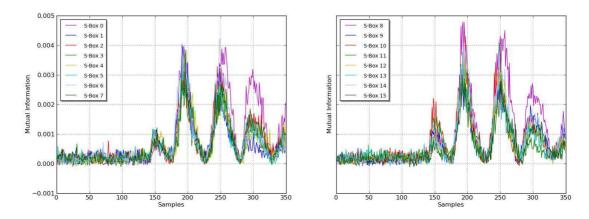

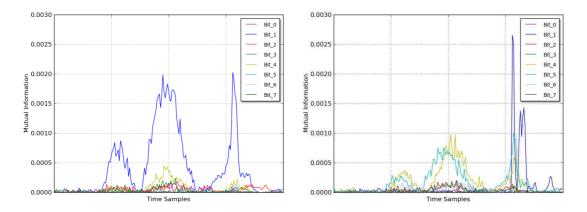

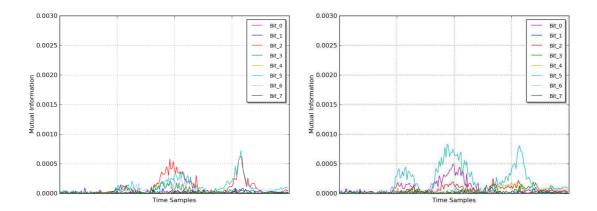

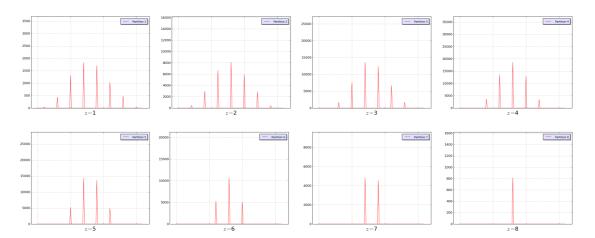

| 4.26 | MIM on the unprotected AES                                                                                 | 81    |

|      | MIM on the BCDL AES.                                                                                       |       |

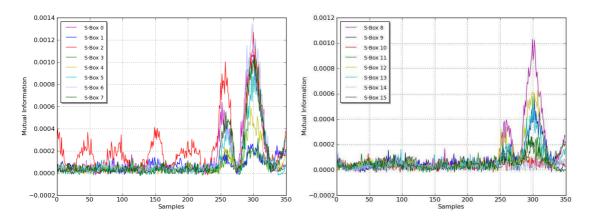

| 4.28 | Mono-bit MIM on BCDL AES S-Box0 (left) and S-Box8 (right)                                                  | 82    |

| 4.29 | Mono-bit MIM on BCDL AES S-Box4 (left) and S-Box7 (right)                                                  | 83    |

|      |                                                                                                            |       |

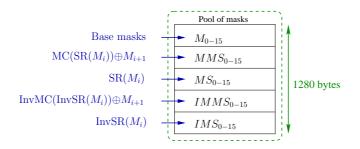

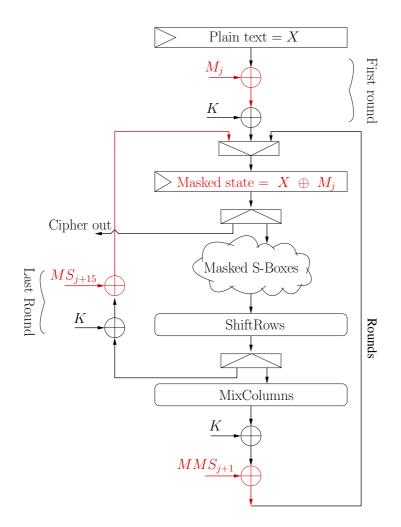

| 5.1  | <i>pdf</i> s of an AES 8-bit register activity with state of the art masking                               | 92    |

| 5.2  | Success Rate and Guessing Entropy for 100 CPA Simulations on an un-                                        | ~ (   |

|      | protected AES.                                                                                             | 94    |

| 5.3  | "State-of-the-Art" Masking <i>pdfs</i> during Simulation on 200000 observa-                                |       |

| - 4  |                                                                                                            | 94    |

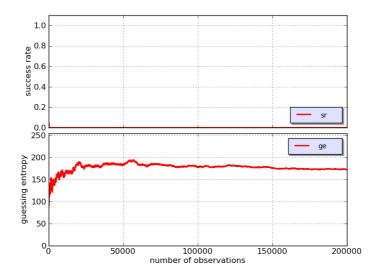

| 5.4  | Success Rate and Guessing Entropy for 100 VPA Simulations on "State-                                       | 05    |

|      | of-the-Art" Masking.                                                                                       |       |

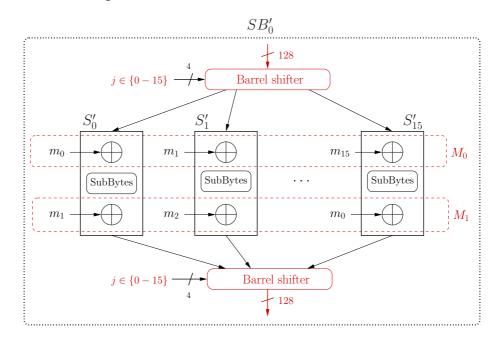

| 5.5  | Revolving S-Boxes.                                                                                         |       |

| 5.6  | Storing masks in ROM/RAM.                                                                                  |       |

| 5.7  | Linear part of the RSM datapath.                                                                           |       |

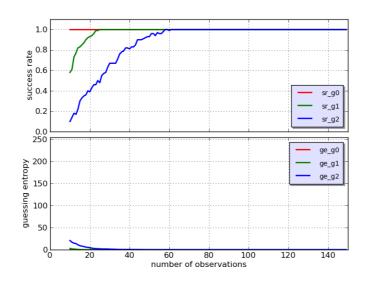

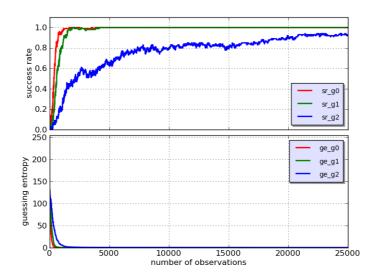

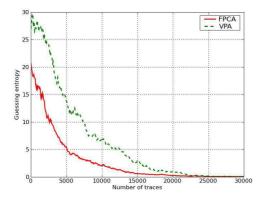

| 5.8  | Success Rate and Guessing Entropy for 100 VPA Simulations on RSM.                                          | 101   |

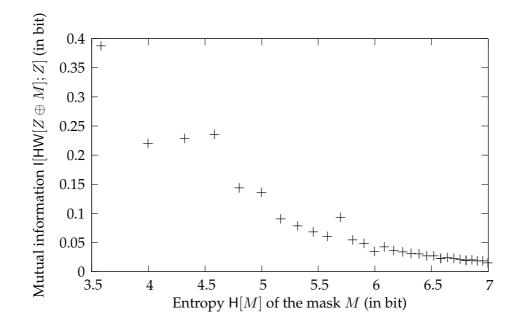

| 5.9  | Mutual information of the leakage in Hamming weight with the sensi- $\begin{pmatrix} 1 \\ 2 \end{pmatrix}$ |       |

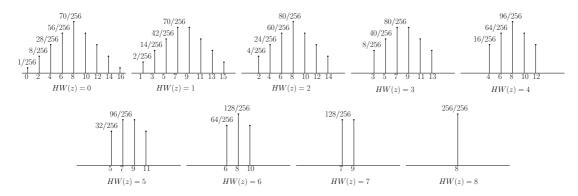

|      | tive variable <i>Z</i> , for one solution that cancels $\rho_{\text{opt}}^{(1,2)}$ found by the SAT-solver | r.115 |

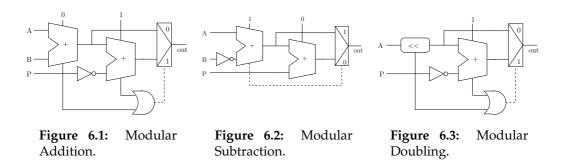

| 6.1  | Modular Addition.                                                                                          | 121   |

| 6.2  | Modular Subtraction.                                                                                       |       |

| 6.3  | Modular Doubling.                                                                                          |       |

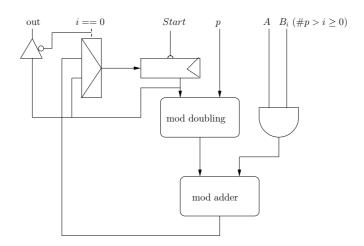

| 6.4  | Modular Multiplication.                                                                                    |       |

| 6.5  | Modular Division/Inversion.                                                                                |       |

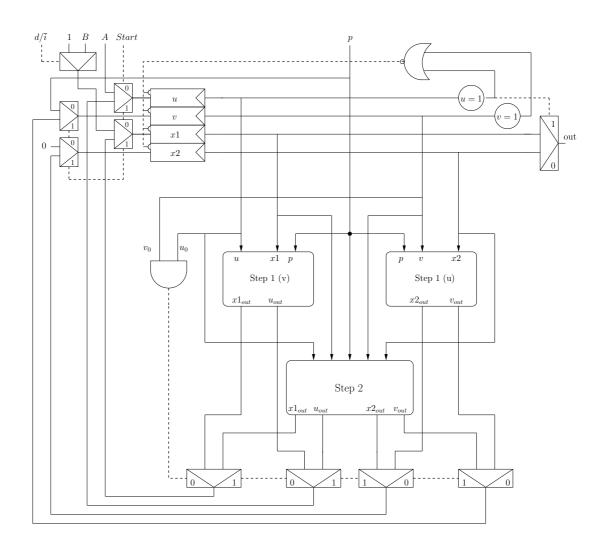

| 6.6  | Modular Division: Step1                                                                                    |       |

| 6.7  | Modular Division: Step2.                                                                                   |       |

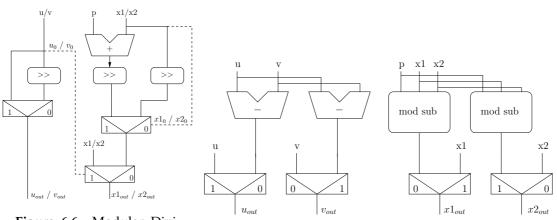

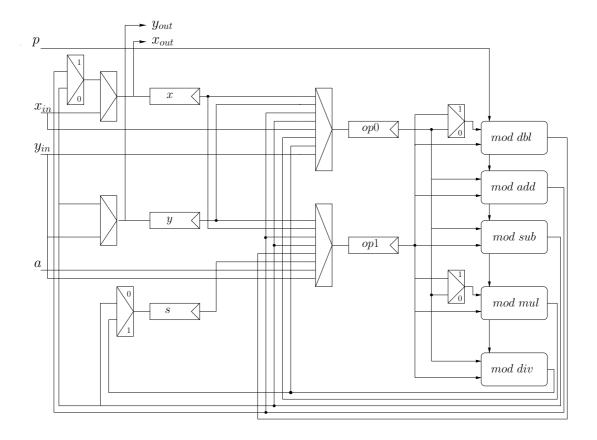

| 6.8  | ECC unprotected datapath.                                                                                  |       |

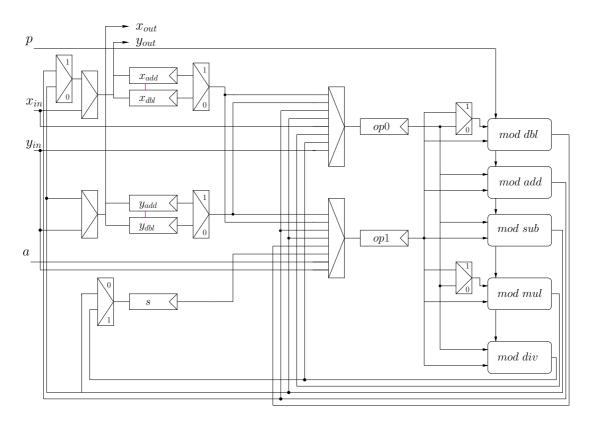

| 6.9  | ECC protected datapath ( <i>Double an Add Always</i> ).                                                    |       |

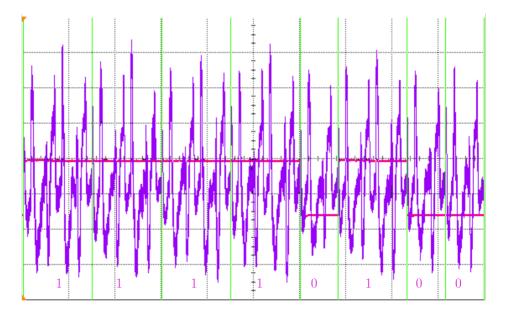

| 6.10 | SPA on unprotected ECC implementation.                                                                     |       |

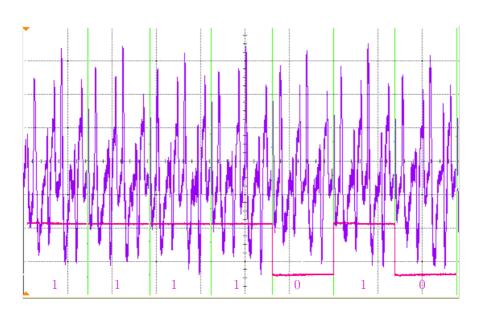

|      | SPA on <i>Double an Add Always</i> ECC implementation.                                                     |       |

|      | Doubling Attack on <i>Double an Add Always</i> ECC implementation                                          |       |

|      | Doubling Attack on ECC implementation with <i>Double an Add Always</i>                                     | 12)   |

| 0.10 | and Scalar Splitting.                                                                                      | 131   |

|      |                                                                                                            | 101   |

#### LIST OF FIGURES

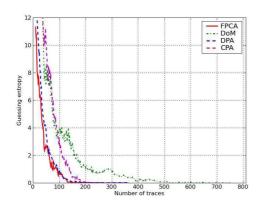

| 7.1  | Unprotected DES guessing entropy metric.                                               | 137 |

|------|----------------------------------------------------------------------------------------|-----|

| 7.2  | Unprotected DES 1st-order success rate metric.                                         | 137 |

| 7.3  | Masked-ROM guessing entropy metric.                                                    | 137 |

| 7.4  | Masked-ROM 1st-order success rate metric                                               | 137 |

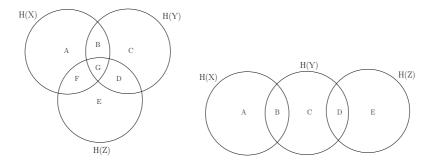

| 7.5  | Venn diagram representation of a case when combination is (a) possible,                |     |

|      | (b) not possible                                                                       | 139 |

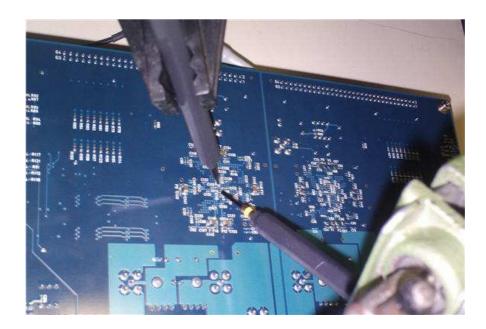

| 7.6  | Placement of antennae for a combined EMA based on combination of                       |     |

|      | measurements                                                                           | 140 |

| 7.7  | Calculation of PC for two cases when combination is (a) possible, (b) not              |     |

|      | possible (mutual information of the two measurements is multiplied by                  |     |

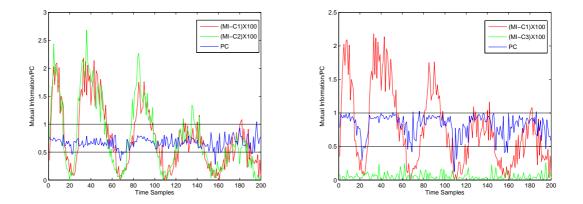

|      | 100 to visualize on the same scale as PC.)                                             |     |

| 7.8  | Leakage function of Sbox 0 (DPA contest v2).                                           | 145 |

| 7.9  | (a) Three correlation coefficients on the leakage function $\mathcal{L}$ , extended in |     |

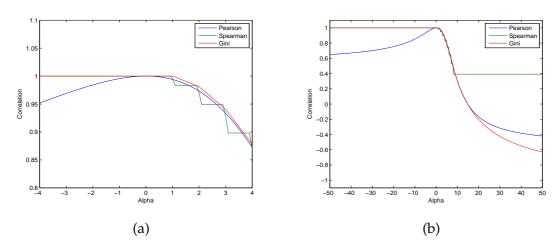

|      | (b) to higher values of $\alpha$ .                                                     | 146 |

| 7.10 | CPA, Spearman vs Combination: (a) Success Rate and (b) Guessing En-                    |     |

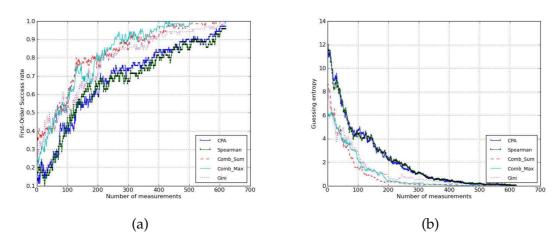

|      | tropy                                                                                  |     |

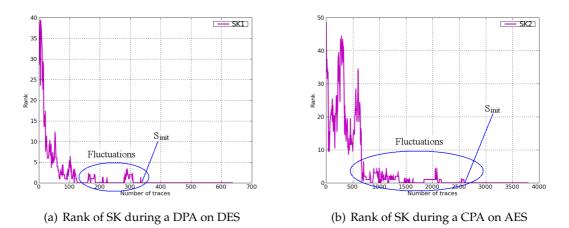

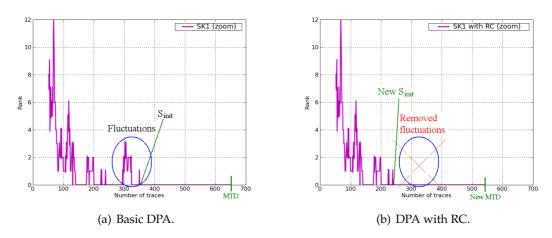

|      | Examples of rank behaviours for the secret key                                         |     |

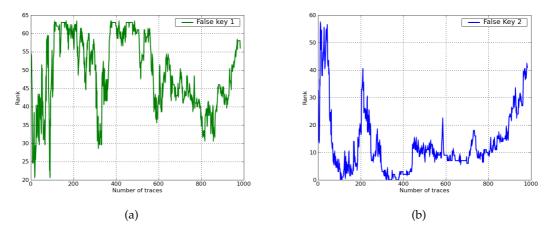

|      | Examples of rank behaviours for false keys                                             |     |

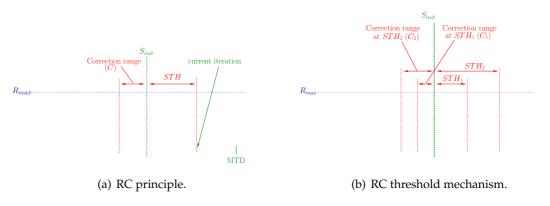

|      | Rank of $SK$ during a DPA, with and without RC                                         |     |

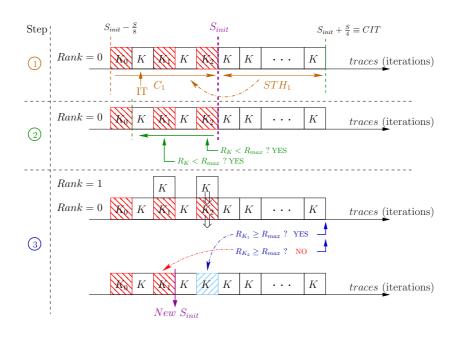

|      | Illustration of RC principle.                                                          |     |

|      | Illustration of an SCA using RC, at the first threshold                                |     |

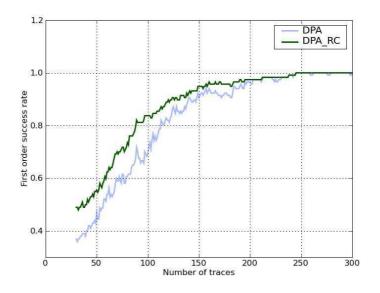

|      | First-order success rate for DPA with and without RC                                   |     |

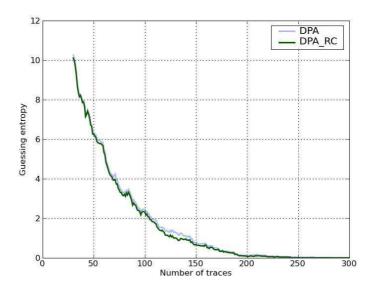

| 7.17 | Guessing entropy for DPA with and without RC                                           | 159 |

|      |                                                                                        |     |

# List of Algorithms

| 1  | Exponentiation Algorithm 5                                      |

|----|-----------------------------------------------------------------|

| 2  | Scalar Multiplication                                           |

| 3  | Square and Multiply Always                                      |

| 4  | Double-and-add always                                           |

| 5  | Montgomery Ladder on RSA                                        |

| 6  | Montgomery Ladder on ECC                                        |

| 7  | "Universal Exponentiation Algorithm" on RSA                     |

| 8  | "Universal Exponentiation Algorithm" on ECC 33                  |

| 9  | Atomic Square and Multiply                                      |

| 10 | BRIP on RSA                                                     |

| 11 | BRIP on ECC                                                     |

| 12 | Blinded Fault Resistant Algorithm on RSA                        |

| 13 | Blinded Fault Resistant Algorithm on ECC                        |

| 14 | Montgomery ladder with randomized addresses                     |

| 15 | Scalar multiplication with Random Elliptic Curve Isomorphism 42 |

| 16 | Modular Multiplication Algorithm                                |

| 17 | Binary Inversion Algorithm                                      |

| 18 | RC detailed algorithm                                           |

| 19 | RC optimization                                                 |

## Glossary

| AES:<br>ASIC:<br>BCDL:<br>CED:<br>CMOS:<br>CPA:<br>CPK:<br>CPK:<br>CRC:<br>CV:<br>DES:<br>DFA:<br>DLP:<br>DoM:<br>DPA:<br>DPA:<br>DPL:<br>DRSL:<br>DWDDL:<br>ECC:<br>EPE:<br>EM: | Advanced Encryption Standard<br>Application Specific Integrated Circuit<br>Balanced Cell based Dual-rail Logic<br>Concurrent Error Detection<br>Complementary Metal Oxide Semiconductor<br>Correlation Power Analysis<br>Current Predicted Key<br>Cyclic Redundancy Check<br>Cumulative Variance<br>Data Encryption Standard<br>Differential Fault Attack<br>Discreet Logarithm Problem<br>Difference of Means<br>Differential Power Analysis<br>Dual-rail with Precharge Logic<br>Dual-rail Random Switching Logic<br>Double Wave Dynamic Differential Logic<br>Elliptic Curve Cryptography<br>Early Propagation Effect |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                  | Current Predicted Key                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                  | <i></i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                  | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                  | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| EN 2.<br>EM:                                                                                                                                                                     | Electro-Magnetic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| EMA:                                                                                                                                                                             | Electro Magnetic Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| FA:                                                                                                                                                                              | Fault Attack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| FK:                                                                                                                                                                              | False Key                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| FPCA:                                                                                                                                                                            | First Principal Component Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| FPGA:                                                                                                                                                                            | Field Programmable Gate Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| GE:                                                                                                                                                                              | Guessing Entropy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| GF:                                                                                                                                                                              | Galois Field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| HD:                                                                                                                                                                              | Hamming Distance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| HW:                                                                                                                                                                              | Hamming Weight                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ICA:                                                                                                                                                                             | Independent Component Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| IMDPL:                                                                                                                                                                           | Improved Masked Dual-rail Precharge Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IP:                                                                                                                                                                              | Intellectual Propertie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| IWDDL:                                                                                                                                                                           | Isolated Wave Dynamic Differential Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LAB:                                                                                                                                                                             | Logic Array Bloc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| LDA:                                                                                                                                                                             | Linear Discriminant Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| LUT:                                                                                                                                                                             | Look-Up Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MDPL:                                                                                                                                                                            | Masked Dual-rail Precharge Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| MIA:                                                                                                                                                                             | Mutual Information Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MIM:<br>MTD:                                                                                                                                                                     | Mutual Information as a Metric                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MTD:<br>NIST:                                                                                                                                                                    | Measurements To Disclose                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| NISI:<br>PAR:                                                                                                                                                                    | National institute of standard and technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PAR:<br>PC:                                                                                                                                                                      | Placement And Routing<br>Possibility of Combination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 201   |                                   |

|-------|-----------------------------------|

| PCA:  | Principal Component Analysis      |

| PK:   | Predicted Key                     |

| RC:   | Rank Corrector                    |

| RAM:  | Random Access Memory              |

| ROM:  | Read Only Memory                  |

| RPA:  | Refined Power Analysis            |

| RSA:  | Rivest Shamir Adleman             |

| RSM:  | Rotating S-Box Masking            |

| S:    | Stability                         |

| SCA:  | Side Channel Attack               |

| SDDL: | Simple Dynamic Differential Logic |

| SE:   | Safe Error                        |

| SG:   | Security Gain                     |

| SK:   | Secret Key                        |

| SNR:  | Signal to Noise Ratio             |

| SPA:  | Simple Power Analysis             |

| SR:   | Success Rate                      |

| STH:  | Stability Threshold               |

| STTL: | Secure Triple Track Logic         |

| VPA:  | Variance Power Analysis           |

| WDDL: | Wave Dynamic Differential Logic   |

| ZPA:  | Zero-value Point Attack           |

# Chapter 1

# Introduction

#### 1.1 Context

As personal and sensitive information are increasingly stored in electronic devices, the need for security grows the same way. Typically, cryptographic devices are used to protect and conceal such data through several algorithms, such as the Advanced Encryption Standard (AES), Rivest Shamir Adleman (RSA) and Elliptic Curve Cryptography (ECC), which are the main focus of this work. Since their introduction, most of them have been thoroughly studied and proven secure from the cryptanalytic standpoint (although research is still ongoing for the ECC). However, in the past few years, a new class of attack have risen, which do not target the mathematical properties of such algorithms but rather their physical implementation itself. Such schemes, best known as Side-Channel Attacks (SCA) pose a very serious threat to secure designs as they are usually low-cost and easy to set-up. As can be expected, the development of SCAs have been coupled with research on appropriate countermeasures. From the sole academic standpoint, a perfect security is generally sought, considering the optimization of area and performances as an important but secondary matter. By contrast, this work operates in an industrial scope, where high level of security and low resource usage are both mandatory. In that regard, the main goal of this thesis is not to find the most secure countermeasure against all possible SCA (as a matter of fact with the present thrive for development of new SCA no countermeasure could be labeled that way), but rather to find the best possible trade-offs between robustness and overheads in terms of area and performances.

#### 1.2 Organization

This document is structured as follows:

#### **1. INTRODUCTION**

In chapter 2 a state of the art of Side-Channel Attacks is drawn, for both symmetrical and asymmetrical algorithms. Passive SCAs, mostly exploiting power, electromagnetic radiations or timing variations as their side-channel leakage are discussed as well as fault injection attacks.

Conversely Chapter 3 deals with the state of the art of SCA countermeasure and their limitations. Schemes targeting symmetrical ciphers, especially the AES are described separately from those aimed at asymmetrical ones, namely RSA and ECC.

The last three chapters present the main contributions of this work. Chapter 4 focus on new countermeasures for symmetrical algorithms and is divided in four parts. First, Section 4.1 gives a detailed study of the vulnerabilities of state of the art DPLs, all the more when implemented on FPGA, illustrated by a successful DPA on a WDDL 3DES. Second, specific constrained placement strategies are proposed in Section 4.2 as a possible way to enhance the security level of DPLs, taking the example of WDDL. Then a new DPL style so-called BCDL is developed in Section 4.3, in the goal of optimizing the trade-off between robustness and resource consumption. A thorough experimental study of that scheme is undertaken putting to light its advantages and weaknesses, then a comprehensive comparison of most known DPLs and their specificity is given in Section 4.4. Eventually the drawbacks of classical masking techniques are highlighted in Section 5.1 before the presentation of a new masking scheme for AES so-called Rotating S-Box masking (RSM) in Section 5.2. Experimental results as well as a thorough theoretical proof (Section 5.3) are then given to validate its security level against SCAs.

An ECC design is implemented in the fourth chapter 4 in order to properly assess that using an FPGA do not induce unexpected vulnerability or resource consumption. Therefore two classical countermeasure, namely the *Double and Add Always* and *random Splitting of Scalar* are implemented on an Altera StratixII. Simple Power Analysis (SPA) as well as *Doubling Attack* (presented in Section 2.2.1) are then performed on the three implementations to experimentally verify their robustness against such SCAs.

In the last chapter 7, three new SCA schemes are introduced. First, a novel attack so-called First Principal Component analysis (FPCA) is described in Section 7.1, using the Principal Component Analysis (PCA) as a side-channel distinguisher. Then two combined SCA are presented that exploit respectively a combination of measurements and distinguishers (Section 7.2 and 7.3). Theoretical and experimental results are given in that regard, showing a significant decrease in the number of side-channel observations or Measurement To Disclose (MTD) needed to perform successful attacks. Finally, a generic algorithm to enhance existing SCAs based on key ranks analysis, so-called *Rank Corrector* (RC) is proposed in Section 7.4. Although this scheme is not an actual attack, it can be combined with most classical SCA and reduce their required number of MTD.

## **Chapter 2**

# Physical Cryptanalysis on FPGA, State of the art

Cryptographic devices are typically used to protect and conceal sensitive data. Although classical algorithms, especially AES, RSA and ECC, are secure from the cryptanalytic standpoint, their actual implementation in hardware designs creates a vulnerability to physical attacks, namely Side-Channel Analysis (SCA) and Fault Attacks (FA).

SCAs and FAs are based on exploiting sensitive information, unintentionally leaked by the target device. There are numerous ways of accessing such information such as monitoring the power consumption or analysing erroneous outputs resulting from fault injection. Globally, a SCA can be characterised by two properties:

- *Passive* or *Active*: a passive attack will not disturb the device's behaviour in any way, while active ones will shift the target from its regular behaviour and analyse its response.

- *Intrusive* or *Non-Intrusive*: Intrusive techniques require physical tampering with the device like depackaging, while non-intrusive schemes only exploit directly available information, for instance the electro-magnetic emanations.

As of now, two categories of physical attacks are mainly studied: on one hand the passive/non-intrusive SCAs which make use of execution time [97], power consumption [98, 115] or electromagnetic radiations [59] as their side-channel and on the other hand active ones, namely FA.

#### 2.1 Generic SCAs

The root of the vulnerability to SCAs lies in the behaviour of CMOS cells of which most recent electronic devices, specially FPGAs, mainly consist of. As a matter of

fact, a clear difference in the power consumption of those elements occurs between a transition from  $0 \stackrel{*}{\rightarrow} 1$  or  $1 \stackrel{*}{\rightarrow} 0$ , when the value changes and one from  $0 \stackrel{*}{\rightarrow} 0$  or  $1 \stackrel{*}{\rightarrow} 1$ , when it does not. This property gives rise to power-based SCAs, as an adversary may be able to observe those transitions via the global activity of the target circuit and use it to retrieve sensitive information. Moreover, one can also exploit the electro-magnetic (EM) field as the side-channel, as they are directly related to the current variations. Unlike power, EM radiations can be collected in a localized manner (depending on the used probe), which may enable the adversary to isolated specific part of the design and reduce the noise ratio. Nonetheless, as most schemes can be conducted using both power and EM measurements, both shall be treated together and referred to as power attacks in the remainder of this manuscript.

In the last few years a wealth of such attacks has been proposed and successfully conducted on several platforms, software and hardware, including FPGAs. They can be classified in two categories: those which exploit a single side-channel measurement, namely Simple Analyses and those which require numerous observations, denoted in the following by Statistical Analyses.

#### 2.1.1 Simple Analyses

Simple Power Analysis (SPA), first introduced by Kocher and al.in [97, 98], relies on the observation of a single side-channel measurement or *trace*. Depending on the type of the target algorithm different information can be retrieved by such schemes. In hardware implementations, when analysing the execution of a block cipher, SPA is generally used to derive some characteristics of the design, for instance the number of rounds, which can in some cases reveal the nature of the algorithm. Figure 2.1 illustrates this behaviour with a SPA of a DES cryptoprocessor, where all the sixteen rounds are clearly visible, within one loading and one output additional cycles.

By contrast, SPA can be an extremal powerful tool to break designs of asymmetrical ciphers, namely RSA or ECC, where no countermeasure against SCAs is implemented. As a matter of fact, those algorithms display a specific iterative behaviour, with regards to the consecutive bits of the secret key. Their respective core operations: the modular exponentiation (Algorithm 1) and the scalar multiplication (Algorithm 2), which are the targets of most SCA, take one key bit into account at each round and perform different computations depending on its value.

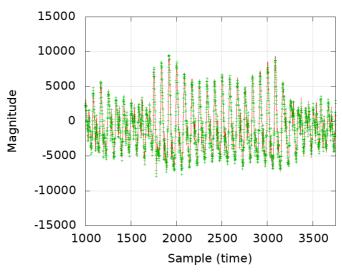

Figure 2.1: SPA on DES.

| Algorithm 1 Exponentiation Algorithm.   | Algorithm 2 Scalar Multiplication.      |

|-----------------------------------------|-----------------------------------------|

| 1: Input: $M, k = (1, k_{l-2},, k_0)_2$ | 1: Input: $P, k = (1, k_{l-2},, k_0)_2$ |

| 2: Output: $Q = M^k$                    | 2: Output: $Q = [k].P$                  |

| 3: $Q \leftarrow M$                     | 3: $Q \leftarrow P$                     |

| 4: for $i = l - 2 \ downto \ 0 \ do$    | 4: for $i = l - 2 \ downto \ 0 \ do$    |

| 5: $Q \leftarrow M^2$                   | 5: $Q \leftarrow 2.Q$                   |

| 6: if $k_i = 1$ then                    | 6: if $k_i = 1$ then                    |

| 7: $Q \leftarrow Q.M$                   | 7: $Q \leftarrow Q + P$                 |

| 8: Return $Q$                           | 8: Return $Q$                           |

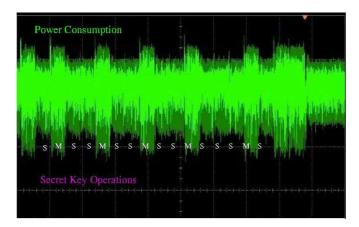

For instance, in Algorithm 1, both a modular multiplication and modular squaring are performed when a key bit is equal to 1, while only the squaring is computed in the other case. Therefore, if an adversary is able to distinguish between the side-channel leakages of those two operations, one measurement is theoretically sufficient to retrieve the entire secret key. An example of SPA on RSA is given in Figure 2.2 to illustrate this behaviour.

Here the two different operations, denoted by *M* and *S* are clearly visible, therefore one can directly deduce the successive value of the processed secret key bits.

In summary, SPA is the most easily mounted SCA, has it only requires one sidechannel measurement (note that in practice, an average of the same trace is performed when possible in order to reduce the noise) and can be used as it stands, without the need of complex analysis software. Therefore providing protection against such scheme is mandatory for device aiming to achieve a high level of security. Fortunately

Figure 2.2: SPA on RSA.

several countermeasures have been proposed to thwart this kind of SCA and will be presented in Section 3.

#### 2.1.2 Timing Attack

The concept of *timing attack* was put to light by Kocher and al. in [97] on software implementations of RSA and applied to hardware smart-card version of this algorithm by Dhem and al. in [52]. Other interesting attack methodology on RSA were presented by Schindler and al. in [150, 153] and by Toth and al. in [179].

The timing attack is a statistical SCA based on exploiting the execution time of a system as the side-channel leakage. As a matter of fact, when the implementation is careless especially in software designs, timing differences correlated to the value of the secret key can appear depending on the value of the inputs. Such correlation can then be exploited to recover a part or even the entire key.

In [153], the authors proven than block ciphers like AES can be broken by such schemes through the exploitation of specific flaws in the architecture, in this case the fact that the execution time of the MixColumns operation can be linked to partial values of the secret. On asymmetrical algorithms like RSA, the attack runs iteratively, recovering one secret key bit at a time. Supposing that the first key bits are known, a set of inputs are generated taking into account both an hypothesis on the value of the next bit and a certain knowledge of the design, such that timing measurement recorded during the corresponding executions will enable the adversary to confirm the validity of this hypothesis. The timing variations can be for instance due to RAM cache hits or branch instructions, in software architectures. In hardware designs those differences are less obvious but can be exploited to mount a successful attack, as shown in [52]. In this paper, the authors used the fact that the Montgomery multiplication, that usually runs in fixed time, will perform a final modular reduction when the intermediate result is too large, hence depending on the input. In the end, they show that given

the right conditions, a 512-bit RSA key can be recovered with 300000 timing measurements and a few minutes of calculation, proving that *timing attacks* poses a real threat to cryptographic devices.

However this kind of SCA requires knowledge of the architecture, to be carried out, as well as having a hand on the input messages. The authors of [52] emphasize that a complete control of the input is not mandatory to mount such attacks. Moreover the adversary must be able to perform precise timing measurements, for instance in [52] the acceptable error margin was of a few clock cycles.

*Timing attack* are not applicable on algorithms running in fixed time, however this property is difficult to ensure, specially for software designs using cache. An other way of thwarting such attacks is to randomize either the key or the input, as will be discussed in Section 3.3.

#### 2.1.3 Statistical SCAs

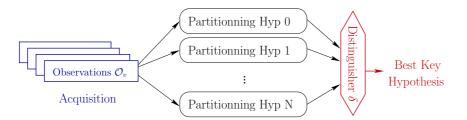

In opposition to the SPA, statistical SCAs require the collection of a large number of measurements, processed with mathematical tools, in order to retrieve the target's secret key. To mount such a successful attack, a few hypotheses must be validated. First, the target algorithm must be known. Second the adversary must be able to at least observe, if not deliberately input, a variable data, which is generally the plaintext in the case of an attack on the first round (e.g. on DES), or the ciphertext when targeting the last round (e.g. on AES). Finally she should seek to uncover a fixed, unknown data, in most cases a part of the secret key (i.e. a sub-key). Then, the goal of such attack is globally to compare and find dependencies between key-dependant estimations of the side-channel leakage and experimental measurements. This leakage is formalized by a model on variable that is correlated to the secret. As illustrated in Figure 2.3, those SCAs usually unfold according to the following scenario:

- 1. Side-channel traces or observations ( $\mathcal{O}_v$ ) are recorded during the execution of the target algorithm. The known variable data (plaintext or ciphertext) is denoted by v.

- 2. Models  $(\mathcal{L}_k)$  of the corresponding leakages are derived for each possible sub-key hypothesis k, based on v.

- 3. Those models are confronted to  $(\mathcal{O}_v)$  by a distinguisher  $\delta$  which sorts those hypotheses and singles out the most probable one.

Those three points denote the critical parts of most SCAs which are the acquisition process, as well as the choice of leakage model and distinguisher.

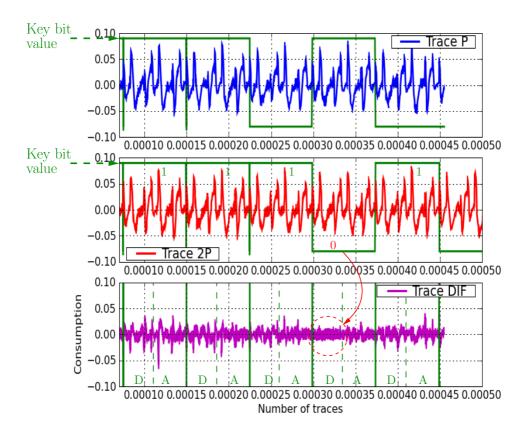

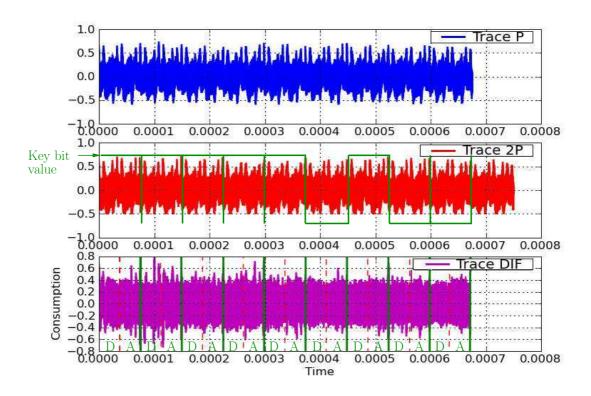

The leakage model, denoted by  $\mathscr{L}$  is the tool used by the adversary to create  $\mathcal{L}_k$ . It targets a key-dependent variable. Most commonly used leakage models are the