# Bandwidth mismatch calibration in time-interleaved analog-to-digital converters

Fatima Ghanem

#### ▶ To cite this version:

Fatima Ghanem. Bandwidth mismatch calibration in time-interleaved analog-to-digital converters. Other. Télécom ParisTech, 2012. English. NNT: 2012ENST0051. pastel-00998759

### HAL Id: pastel-00998759 https://pastel.hal.science/pastel-00998759

Submitted on 2 Jun 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **Doctorat ParisTech**

### THÈSE

pour obtenir le grade de docteur délivré par

#### **TELECOM ParisTech**

Spécialité « Electronique et Communications »

présentée et soutenue publiquement par

#### **Fatima GHANEM**

le 28 septembre 2012

## Compensation de l'erreur de bande passante dans les

### convertisseurs analogique numérique à entrelacement temporel

Directeur de thèse : Patrick LOUMEAU

Co-encadrement de la thèse : Patricia DESGREYS

#### Jury

M. Amara AMARA, Professeur, ISEP, Paris

M. Dominique DALLET, Professeur, IMS, Bordeaux

M. Philippe BÉNABÈS, Professeur, Supélec, Paris

M. M. Philippe GANDY, Reponsable, IDT, Caen

M. Arnaud BIALLAIS, Ingénieur, IDT, Caen

M. Patrick LOUMEAU, Professeur, IT ParisTech, Paris

Mme. Patricia DESGREYS, Maitre de Conférences, IT ParisTech, Paris

Président

Rapporteur

Rapporteur

Examinateur

Examinateur

Directeur de thèse

Co-directrice de thèse

## Remerciement

Ma thèse de doctorat s'est effectuée entre le département Electronique et Communications à Telecom ParisTech où j'ai passé les 18 premiers mois de ma thèse ainsi que l'équipe convertisseurs au sein de IDT/ NXP France où j'ai terminé ma thèse.

Je tiens tout d'abord à remercier Mes directeurs de thèse Patrick Loumeau et Patricia Desgrey pour leur disponibilité et leur confiance durant ma thèse. Merci à mon ancien encadrant de thèse Christophe Erdmann, qui m'a poussé à aller de l'avant et a partagé son savoir faire.

Cette thèse n'aurait pu aboutir sans l'aide de Arnaud Biallais et ses critiques très constructives, merci beaucoup à toi.

Ma grande gratitude va à Philippe Gandy qui a toujours cru en moi et m'a soutenue dans toutes mes épreuves, tes conseils me sont précieux, quel qu'en soit le domaine merci!

J'adresse également mes remerciements à Philippe Benabès et Dominique Dallet qui ont eu un regard critique en rapportant sur ma thèse, cela m'a été très utile. Merci à Mr Amara Amara qui a accepté de présider la soutenance de ma thèse, c'était un honneur.

Merci à Chadi Jabbour, mon soutien à Télécom Paris de qui j'ai beaucoup appris sur les convertisseurs et surtout merci pour les chocolats et les gâteaux que tu nous ramenais, je les regrette beaucoup. Merci également à Hussein Fakhoury qui est un exemple de motivation accrue au sein de l'équipe de TelecomParisTech. J'adresse également mes remerciements à mes anciens collègues avec qui je déjeunais tous les jours et avec qui je partageais mon quotidien à Télécom ParisTech : Germain, Asma, Ali, Arwa, Alban, Pietro, Hasham, Mariam, Melanie, Sami, Cyrius, Aziz, Zahir, Shivam et j'en oublie d'autresĚ J'ai eu la grande chance de finir ma thèse au sein d'une famille à Caen, l'équipe convertisseurs.

Je n'oublierai jamais l'accueil qui m'a été réservé, la générosité des gens, le partage de leur savoir, de leurs conseils et de la bonne humeur de tous les jours. Merci à vous tous, Denis V pour tes dessins et tes blagues très subtiles et Thierry et tes informations croustillantes, Nabil et ton panache surtout après une victoire de Lyon, È ça a été longtemps mon équipe préférée Merci à Stephane B pour ton aide et Lionel pour ton optimisme, il en faut beaucoup dans cette vie Merci à Jean-Pierre, Olivier G, Fabrice, à Luis, notre espagnol, Olivier H notre syndic préféré et merci à Hervé et Philippe B pour les sorties footing qui libèrent la tête Merci à toi Sylvain, te revoilà le plus jeune mais avec un immense potentiel. Merci à Arnaud K, le apple geek, à Luc, Denis C, Arnaud B, le box n'aurait pas été aussi bien sans vous, ce qui ne me fait pas regretter mon choix de digital:).

Je n'oublie pas de remercier Sophie, tu es un exemple de réussite pour les femmesÉ et merci à Jean Michel qui m'a accepté dans cette famille. Enfin, je tiens à remercier notre

chère aimable et généreuse secrétaire Fabienne. Merci aussi à Micky pour ton aide pour les mesures, qu'on a enfin réussi à faire É et merci à Franck pour ta disponibilité.

Il ne m'aurait jamais été possible d'aller au bout de cette thèse sans ton aide inestimable et ton éternel soutien. A toi mon époux 'Nabil' je ne saurais te dire merci!

ET bien sur, j'adresse cette réussite à ma famille et particulièrement à mes parents Zakia et Hamadi, pour les valeurs que vous m'avez inculquées et de la confiance que vous m'avez accordée depuis ma plus jeune enfance. Je vous dédie ma thèse!

## Résumé en Français

#### I Introduction

Le nombre important de standards pour la communication sans fil déjà présent sur le marché (GSM, EDGE, TDS-CDMA, WCDMA), ainsi que tous les futurs standards en développement (HSPA, LTE) poussent les ingénieurs système à développer des émetteurs récepteurs extrêmement flexibles pouvant s'accommoder de plusieurs standards différents. Ceci est particulièrement vrai dans les stations de base où le coût d'un redéploiement de station de base est important. C'est le but ultime des " software programmable system " où le traitement analogique est minimisé, ce qui signifie que le traitement spécifique des standards est réalisé en programmant la partie numérique.

D'autres part, la demande grandissante des utilisateurs à accéder à des applications multimédia via leurs téléphones portables, ordinateurs portables ou tablettes poussent les opérateurs à proposer des réseaux cellulaires avec une plus en plus grande capacité de débit. Il est indispensable pour les opérateurs d'offrir des réseaux alliant un débit plus important et un contrôle drastique de la consommation énergétique. Un des défis pour les fournisseurs d'infrastructures de réseaux cellulaires sans-fils est donc de fournir des équipements offrant plus de débit, moins de consommation énergétique et une compatibilité entre les différents standards. Un des points d'attention pour la puissance dissipée étant la chaine de transmission.

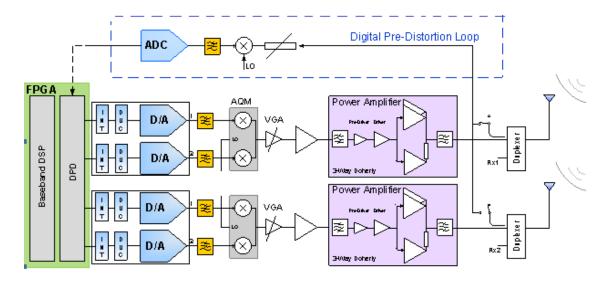

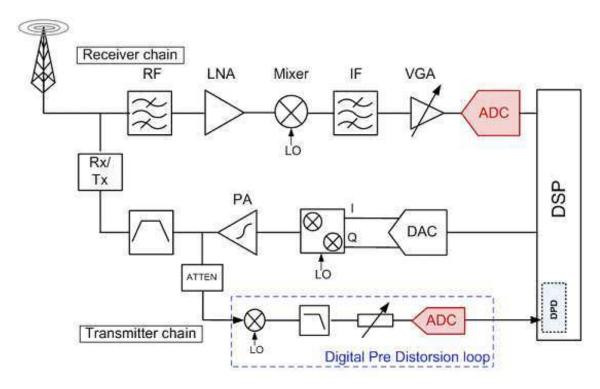

Figure 1 – Schéma bloc d'une chaîne de transmission

La Figure 1 représente l'architecture d'une chaine de transmission la plus couramment utilisée dans les stations de base. Le convertisseur Analogique Numérique faisant l'interface entre le monde, il est très important qu'il soit le plus fidèle à l'information transmise. En effet, transmettre plus d'information nécessite une bande d'utilisation plus large. Pour le convertisseur analogique-numérique (CAN/ADC), cette augmentation de la bande passante implique l'intégration de plus de bruit thermique des étages précédents dans la chaine radio, ce qui diminue la dynamique d'entrée du convertisseur. Pour palier à ce problème et diminuer le plancher de bruit d'une chaîne de réception, deux solutions :

- augmenter la fréquence d'échantillonnage du CAN,

- diminuer le bruit total du convertisseur, en travaillant à la fois sur le bruit thermique et le bruit de quantification (en augmentant sa résolution).

Pour le CAN, et à linéarité constante, il est aussi difficile de réaliser l'une ou l'autre de ces solutions. Le but des travaux de thèse décrits dans ce document est d'étudier et de concevoir un CAN haute vitesse (500Msps), haute résolution (16 bits) pour des applications station de base, et plus particulièrement dans la chaîne de réception. Ce CAN devra avoir d'excellentes performances statiques et dynamiques, une très large bande passante, tout en ayant une consommation en puissance, ce qui permettra une meilleure intégration. Le tableau ci-dessous résume alors les paramètres clés pour le convertisseur à réaliser pour les deux modes de transmission émission (Tx) et réception (Rx); à savoir : la vitesse (fréquence d'horloge), la résolution (spécifiée par le SNR), la puissance dissipée du convertisseur et le SFDR.

| Application         | Speed  | Resolution | SNR           | SFDR          | Conso |

|---------------------|--------|------------|---------------|---------------|-------|

|                     | (Msps) | (bits)     | (dBFS)        | (dBc)         | (mW)  |

| Station de base(Rx) | 500    | 14/16      | $73_{10MHz}$  | $94_{10MHz}$  |       |

|                     |        |            | $73_{380MHz}$ | $90_{380MHz}$ | < 650 |

| Station de base(Tx) | 500    | 12/14      | $67_{10MHz}$  | $88_{10MHz}$  |       |

|                     |        |            | $65_{380MHz}$ | $85_{380MHz}$ |       |

Table 1 – Spécification du convertisseur hautes performances à réaliser.

### II Choix de l'architecture et description du problème

#### II.1 Etat de l'art

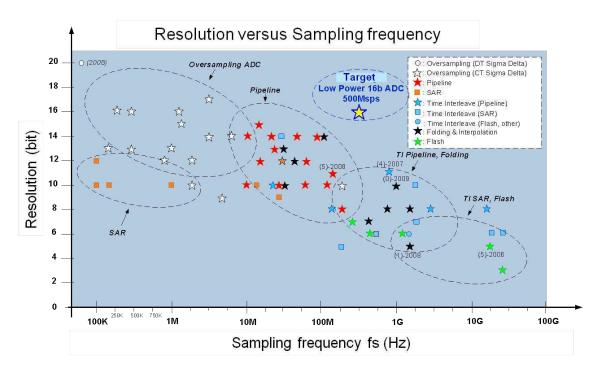

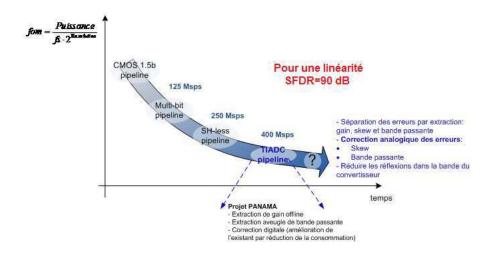

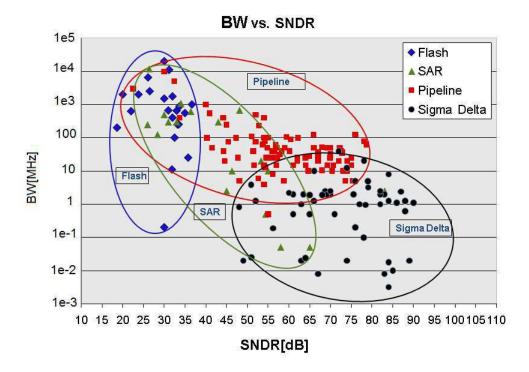

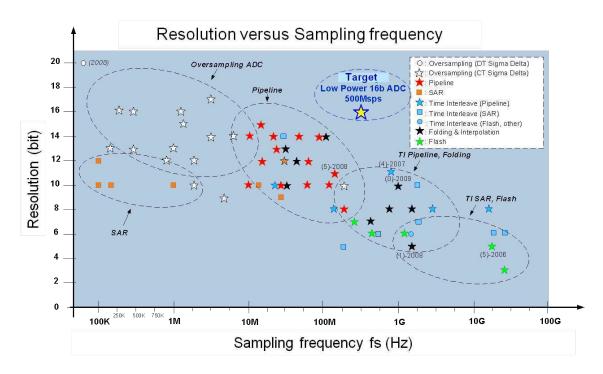

Afin de choisir une architecture adéquate à l'application visée et être compatible avec le niveau d'exigence des spécifications (combinant linéarité, rapport signal-sur bruit, bande passante élevée et faible puissance), un état de l'art a été effectué sur les CANs existants. Celui-ci a permis une comparaison des différentes architectures les plus utilisées dans le marché depuis les années 2000, à savoir le Flash, Folding, le Pipeline, le SAR et le Sigma Delta (Figure. 2). Il apparaît alors que le pipeline est l'architecture qui se distingue le plus par sa haute vitesse pour des résolutions élevées. Par ailleurs, la figure montre qu'il existe un compromis vitesse/résolution pour cette architecture et que pour des résolutions de 16 bit, on ne dépasse pas la vitesse de 20Msps.

FIGURE 2 – Resolution vs. Vitesse des ADCs dans la littérature (IEEE Journal of Solid-State Circuits, ISSCC International Solid-State Circuits Conference, IEEE transaction on Circuits and System, ESSCIRC, European Solid-State Device Research)

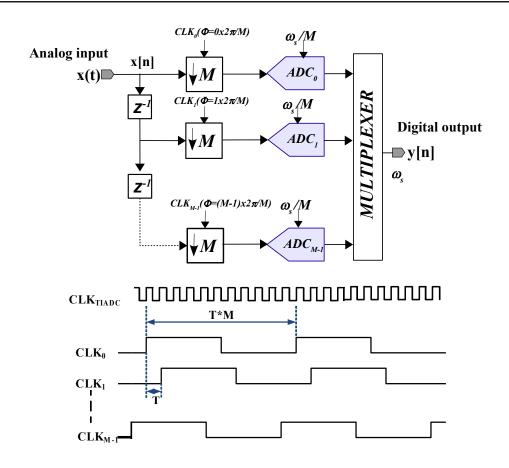

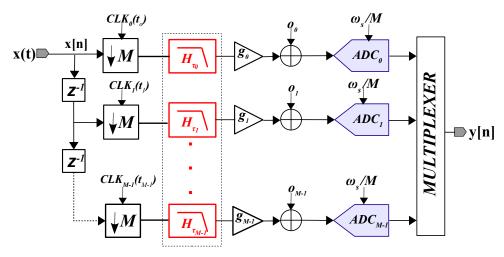

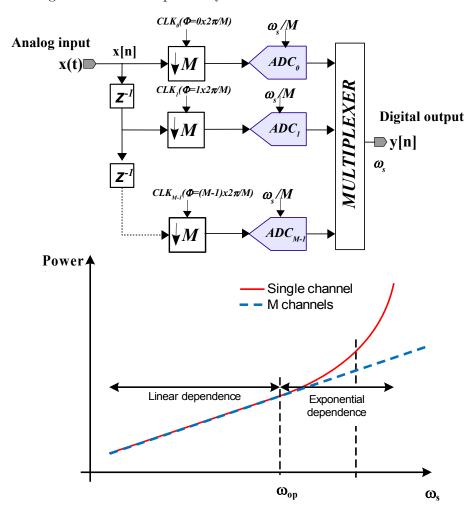

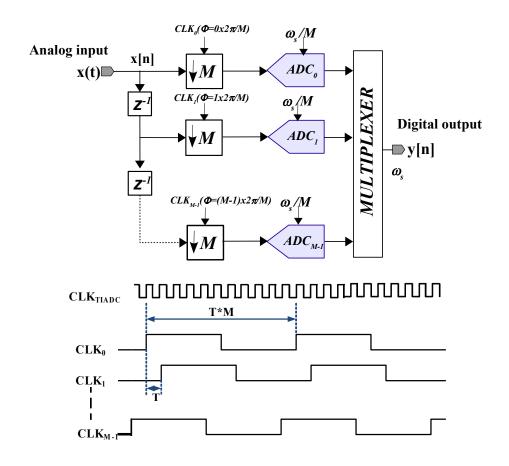

Le principe de fonctionnement de cette architecture est décrit dans la Figure. 3 où le signal d'entrée  $\mathbf{x}(t)$  est converti successivement par chacun des convertisseurs et est ensuite reconstruit à l'aide d'un multiplexeur. Ceci permet alors de multiplier la vitesse d'une voie par le nombre de canaux pour avoir une fréquence d'échantillonnage plus élevée  $(f_s)$ . De ce fait, et puisque la vitesse souhaitée de 500 Msps pour un convertisseur pipeline à 16 bits de résolution est à atteindre, le choix de l'architecture à entrelacement temporel (TIADC) peut s'avérer judicieux.

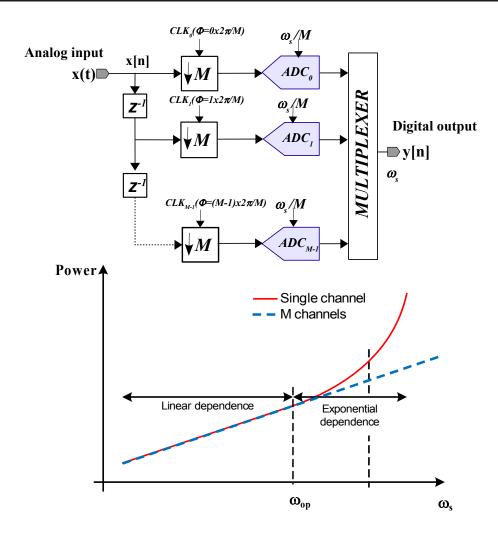

De plus, et afin d'atteindre les performances en consommation souhaitées, le CAN à entrelacement temporel est le meilleur choix architectural pour des fréquences d'opération élevées. En effet pour un noeud technologique donné, la Figure. 4 montre que la puissance consommée par un convertisseur monocanal varie exponentiellement avec la fréquence d'échantillonnage. L'architecture à entrelacement temporel profite alors de la caractéristique linéaire de la puissance consommée de chacune des voie en fonction de la vitesse et par conséquent la puissance dissipée est le produit de la consommation d'une seule voir par le nombre de canaux.

De ce fait, l'architecture à entrelacement temporel combine de bonnes performances en vitesse et en puissance dissipée, ce qui semble être le meilleur choix pour adresser notre problème.

#### II.2 Convertisseur analogique numérique à entrelacement temporel

L'entrelacement temporel, bien qu'ayant les avantages comme la vitesse ou la consommation dissipée, présente toutefois des imperfections dues aux mésappariements entre les

Figure 3 – Convertisseur à entrelacement temporel.

voies liés aux changements de l'environnement. Les quatre erreurs les plus connues sont : le décalage en tension (offset), le gain, l'erreur de l'instant d'échantillonnage (skew) et l'erreur de bandes passantes entre les filtres d'entrée des différents convertisseurs.

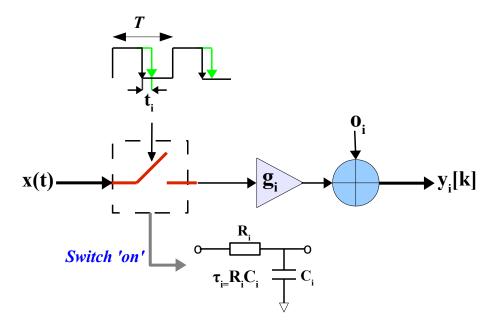

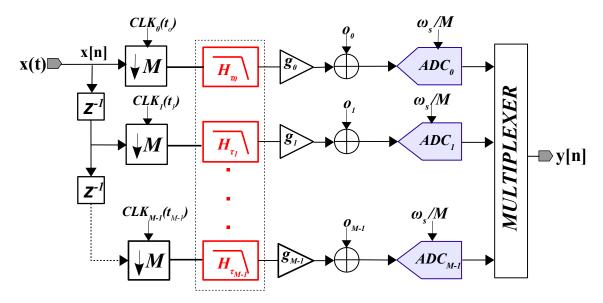

Soit alors M convertisseurs CANs entrelacé, chacun fonctionnant à une vitesse  $\omega_s/M$  (Figure 2.4), la sortie de chaque voie i constituant le convertisseur à entrelacement temporel notée  $y_i$  et est exprimée par :

$$y_i[k] = g_i x ((kM+i)T - t_i) * h_{\tau_i}(t) + o_i.$$

(1)

où  $o_i$  représente l'erreur d'offset du canal i,  $g_i$  l'erreur de gain,  $t_i$  l'erreur de l'instant d'échantillonnage et  $H_{\tau_i}$ , le filtre d'entrée de chaque voie. La réponse en fréquence de la sortie globale incluant toutes les erreurs est donnée par :

$$Y(e^{j\omega}) = \frac{1}{T} \sum_{k=-\infty}^{+\infty} \left[ \frac{1}{M} \sum_{i=0}^{M-1} g_i H_i (j(\omega - k \frac{\omega_s}{M})) e^{-j(\omega - k \frac{\omega_s}{M})t_i} \cdot e^{-jki \frac{2\pi}{M}} \right] X(j(\omega - k \frac{\omega_s}{M}))$$

$$+ \frac{1}{T} \sum_{k=-\infty}^{+\infty} \frac{1}{M} \sum_{i=0}^{M-1} o_i e^{-jki \frac{2\pi}{M}} \delta(\omega - k \frac{\omega_s}{M}).$$

$$(2)$$

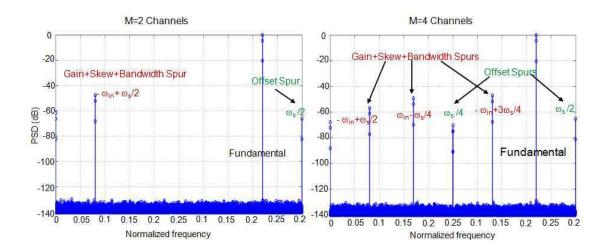

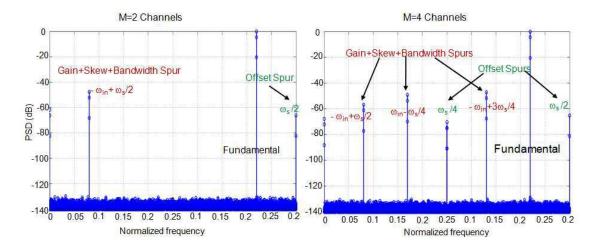

L'impact de ces erreurs sur le spectre de sortie est représenté sur la Figure. 6, où nous voyons apparaître des raies de distorsion pour 2 et 4 canaux. Il faut noter que le nombre

$\label{eq:figure} {\it Figure 4-Convertisseur\ a\ entrelacement\ et\ consommation\ pour\ un\ noeud\ technologique\ donné.}$

Figure 5 – CAN à entrelacement temporel à M canaux.

de raies de distorsion dépend du nombre de voies. Il est aussi montré sur cette figure que l'offset est une erreur qui est indépendante du signal d'entrée et apparait tous les  $\omega/M$  ce qui rend sa compensation assez triviale [34,35].

En ce qui concerne les erreurs de gain, skew et l'erreur de bande passante, elles génèrent des raies de distorsion aux fréquences  $\pm \omega_{in} + k \frac{\omega_s}{M}$ .

FIGURE 6 – Impact des erreurs à la sortie d'un CAN a entrelacement temporel.

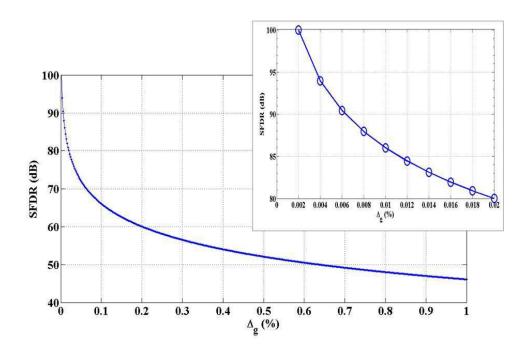

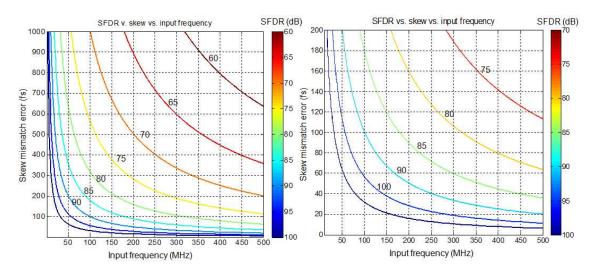

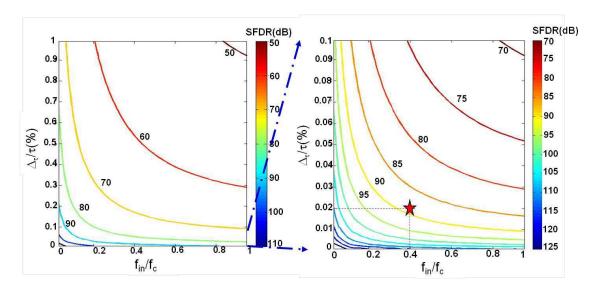

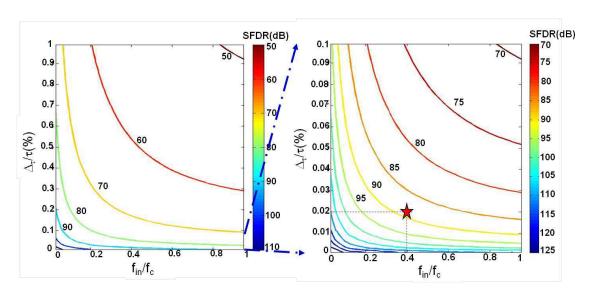

De ce fait, la linéarité du convertisseur, représentée par le SFDR, est dégradée par la raie de distorsion la plus élevée. Il devient alors nécessaire de compenser les erreurs d'appariements afin que le convertisseur atteigne les performances visées. Des abaques ont alors été tracés afin de définir les résolutions nécessaires pour les différentes erreurs afin d'atteindre les performances en SFDR visées.

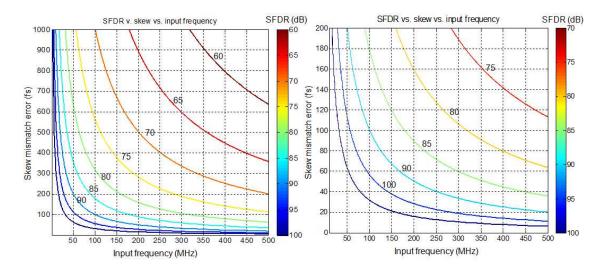

La figure 2.6 montre que l'erreur de gain ne doit pas dépasser les 0.006% entre deux canaux d'un convertisseur à entrelacement temporel, tandis que le skew doit être inférieur à 25 fs afin d'avoir un SFDR >90 dB pour des fréquences élevée (380 MHz) (Figure. 8).

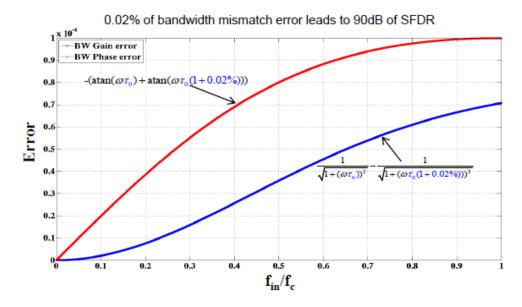

Dans la littérature, plusieurs travaux visent à compenser ces deux erreurs (gain et skew) et permettent alors d'atteindre de bonnes performances [7,8,9,35,36,37,45,47]. Cependant, l'erreur de bande passante apparaissant avec les applications très larges bandes peut altérer ces corrections des erreurs de gain et de skew. En effet, l'erreur de bande passante est causée par les appariements entre les filtres d'entrée des canaux constituant le convertisseur à entrelacement temporel. Elle présente des contributions en gain et en phase qui dépendent de la fréquence d'entrée ce qui rend la calibration aveugle plus difficile à réaliser. Très peu de travaux traitent cette erreur et à ce jour, à notre connaissance aucune méthode d'extraction de cette erreur n'a été proposée dans la littérature. Nous nous sommes alors intéressés à cette erreur et des solutions analogiques et numériques ont été proposées durant la thèse pour compenser l'erreur de bande passante.

FIGURE 7 – SFDR versus erreur de gain statique.

FIGURE 8 – SFDR versus erreur de skew.

#### III Erreur de bande passante dans un TIADC

#### III.1 Analyse de l'erreur de bande passante

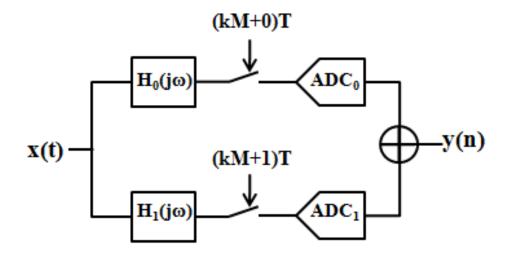

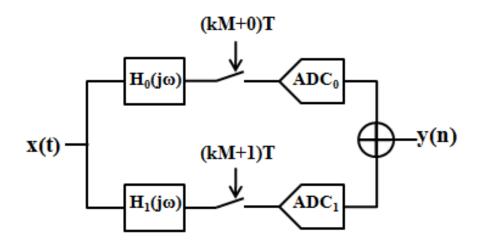

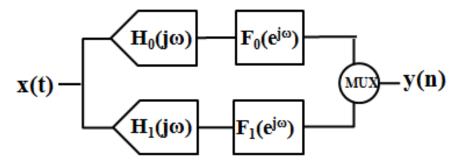

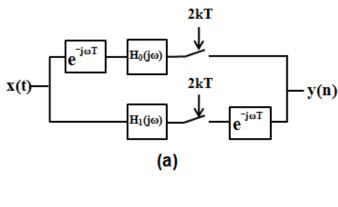

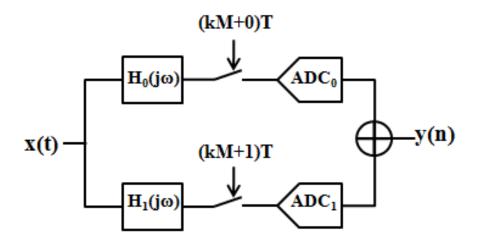

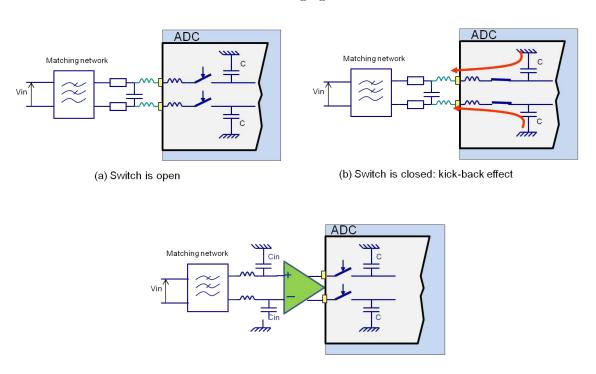

Pendant la phase d'échantillonnage, chaque réseau d'entrée à capacités commutés se comporte comme de filtre passe. Pour un convertisseur à entrelacement temporel à deux voies, nous représentons pas  $H_0$  et  $H_1$ , les filtres d'entrée ayant des fréquences de coupures différentes (Figure 9).

L'hypothèse de notre étude est de considérer un filtrer passe bas de premier ordre et la

FIGURE 9 - CAN à entrelacement temporel à deux canaux.

sortie de chaque CAN i s'exprime par :

$$y_i[k] = (g(\tau_i))x((kM+i)T + f(\tau_i)).$$

(3)

Où  $\tau_i$  représente la constante de temps et

$$\begin{cases} g(\tau_i) &= \frac{1}{\sqrt{1 + (\omega \tau_i))^2}}, \\ f(\tau_i) &= -\arctan(\omega \tau_i). \end{cases}$$

(4)

Le gain et la phase dus au filtrage d'entrée.

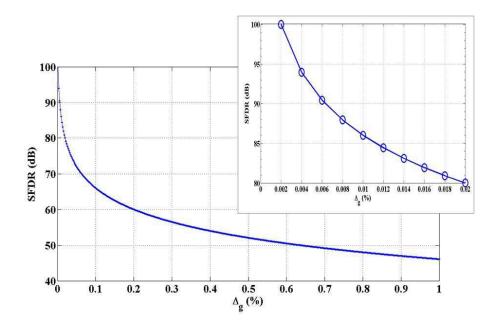

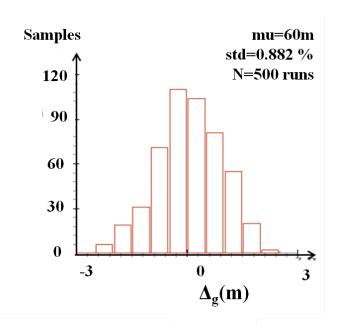

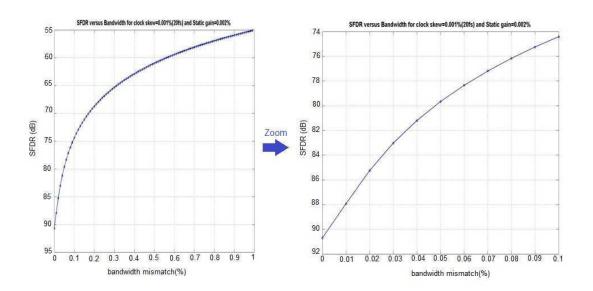

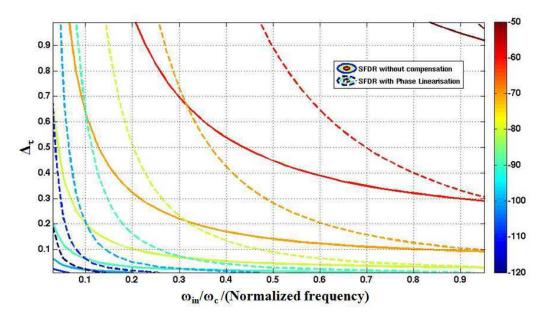

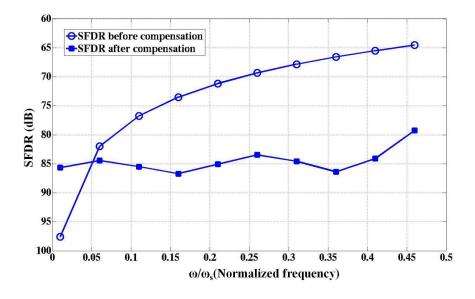

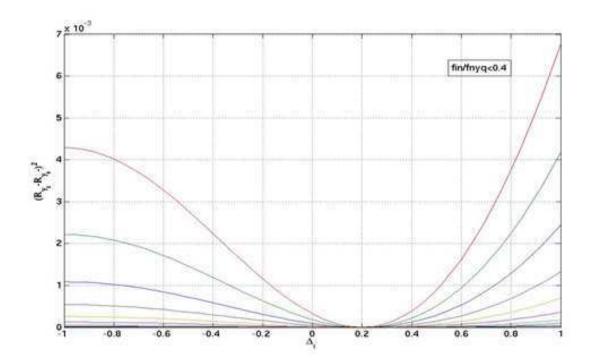

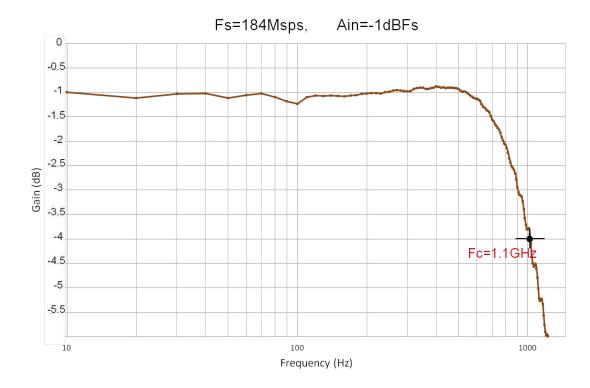

L'impact de cette erreur sur les performances en SFDR en fonction de la fréquence est présenté sur la Figure. 10 et permet de spécifier la résolution souhaitée pour atteindre les performances souhaitée. En effet, pour l'application station de base visée, l'erreur de bande entre deux canaux ne doit pas dépasser 0.02% pour des fréquences d'entrée jusqu'à 384MHz (ici la fréquence de coupure de moyenne est de 1.1 GHz). Cependant, des simulations Monte Carlo montrent que l'erreur d'appariement entre les filtres d'entrée dans un circuit peut dépasser 2% ce qui dégrade fortement les performances.

## III.2 Contributions et Techniques de calibration de l'erreur de bande passante

Une fois la spécification en termes d'erreur de bande établie, deux modes de calibration ont été considérés afin proposer des solutions de calibration de l'erreur de bande passante :

Considérer les erreurs séparées : cela supposerait alors que les erreurs sont indépendantes et donc peuvent être traitées séparément. Or, l'erreur de bande apparaît dans le gain et la phase du signal de sortie et ces composantes dépendent de la fréquence d'entrée de façon non linéaire. D'autre part, ces contributions en gain et en phase dûes à la bande s'ajoutent respectivement au gain statique et au skew. Par conséquent, l'application des techniques de calibration aveugles de gain et de skew proposées dans la littérature deviennent obsolètes et sont gênées par la présence de l'erreur de bande passante. En effet, les simulations ont montré qu'en considérant des erreurs séparées,

FIGURE 10 – SFDR versus erreur de bande passante.

le SFDR de 85 dB est atteint pour chacune des résolutions de 0.001% d'erreur de gain, 25 fs d'erreur de skew et 0.02% d'erreur de bande passante. Cependant l'application successive des corrections de gain, skew puis la bandes passante en présence de toutes les erreurs et pour les mêmes résolutions nous donne un SFDR de 70 dB. En conséquence, il est important que les techniques appliquées pour les corrections de gain et de skew intègrent l'erreur de bande et pour se faire, une estimation de l'erreur de bande d'une façon dissociée des autres erreurs est impérative afin que les solutions de correction de skew et de gain soient applicables.

– Le deuxième cas prévoit une estimation de l'erreur globale incluant le gain, le skew ainsi que l'erreur de bande passante limitant ainsi le mode de correction à une correction numérique [18]. Pour les résolutions déjà évoquées (0.006% pour le gain, 25 fs pour le skew et 0.02% pour l'erreur de bande passante), la taille de filtres de correction devient très importante ramenant la consommation du bloc de correction à plus de 200 mW, ce qui représente un grand pourcentage comparé à la consommation visée (620 mW). Il est alors préférable de considérer une correction analogique permettant d'avoir une puissance globale dissipée plus faible. Cependant, la méthode d'estimation de l'erreur globale n'est pas adaptée à une correction analogique où les erreurs sont traitées séparément.

Suite aux limitations que présentent les solutions existantes pour la calibration de l'erreur de bande, nous avons proposé des solutions pour améliorer le SFDR ainsi que la consommation visée, tout en garantissant une vitesse d'opération globale de 500 Msps.

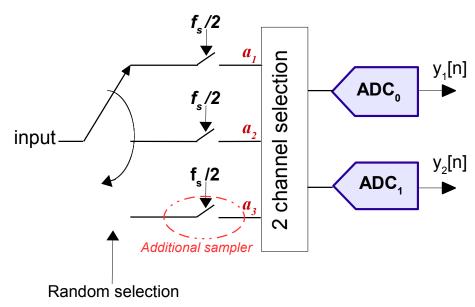

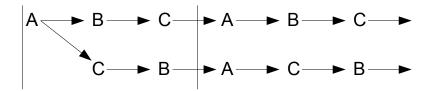

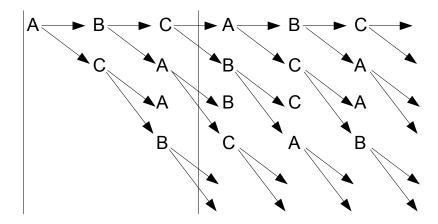

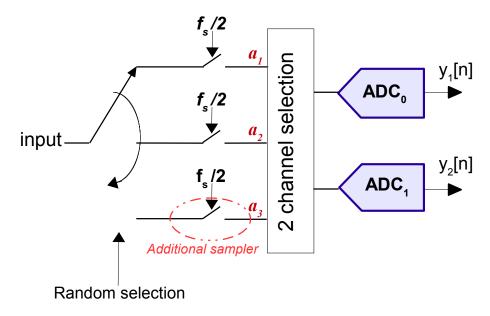

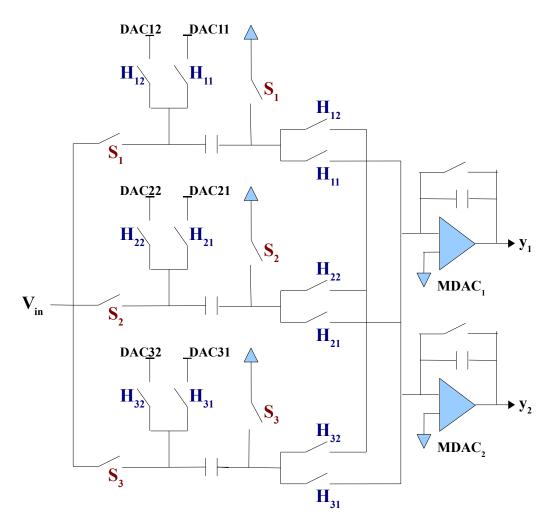

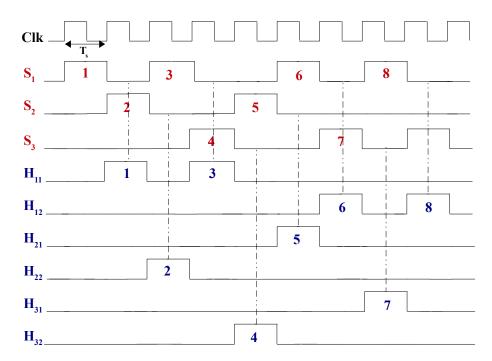

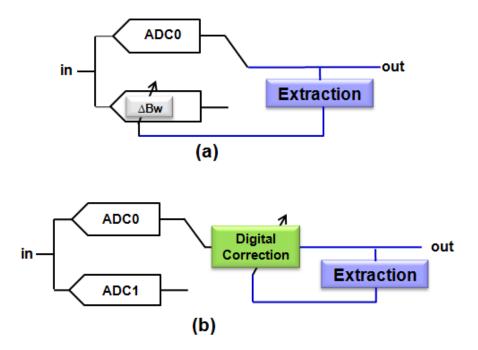

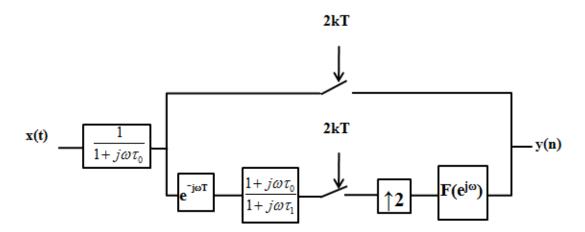

#### 1. Randomisation des réseaux d'échantillonnage

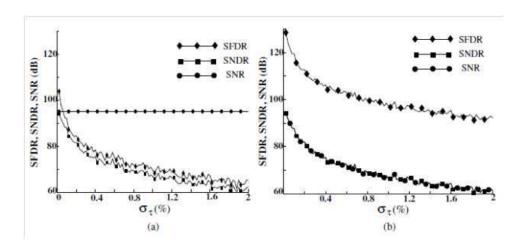

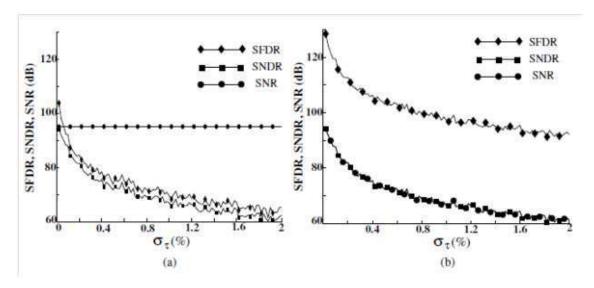

Cette solution analogique consiste à ajouter un ou plusieurs réseaux d'échantillonnage afin de randomiser l'effet cyclique de l'erreur de bande dans l'architecture à entrelacement temporel. Le modèle proposé est décrit dans la Figure. 11. Ceci permet d'étaler les raies parasites sur toute la bande et donc d'améliorer le SFDR, cependant la puissance de bruit globale reste constante comme le montre la Figure. ??. Cette solution se distingue de l'existant où des canaux entiers sont ajoutés pour effectuer la randomisation et donc consommerait plus de puissance et de surface [TS01]. Cependant, la solution que nous proposons est plus adaptée aux erreurs suffisamment petites afin

que le bruit ajouté ne dégrade pas suffisamment le SNR.

Figure 11 – Modèle de randomisation des réseaux d'échantillonnage proposé.

FIGURE 12 – Amélioration du SFDR après randomisation des réseaux d'échantillonnage d'entrée.

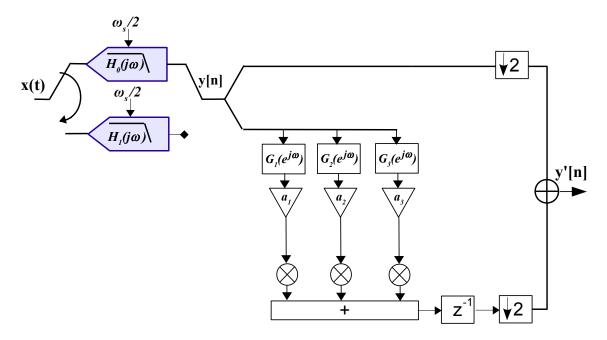

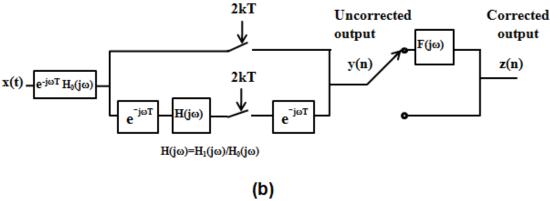

#### 2. Compensation de l'erreur de bande passante :estimation et correction

Une seconde démarche consiste à extraire l'erreur de bande d'une façon numérique et la corriger; soit en analogique. Il n'existe à ce jour aucune solution qui permet d'estimer l'erreur de bande d'une manière aveugle. En effet, seulement deux solutions traitent cette problématique d'estimation. La première, semi aveugle, utilise un signal additionnel pour extraire l'erreur [18]. La seconde, propose une estimation globale; c'est-à-dire de toutes les erreurs [69]. Cependant, cette dernière ne permet pas une correction analogique des erreurs; ce qui est préféré à la correction numérique qui présente une puissance consommée plus élevée.

#### - a. Principe de fonctionnement

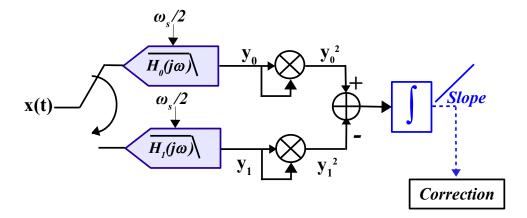

La solution d'extraction proposée dans cette thèse de l'erreur de bande passante

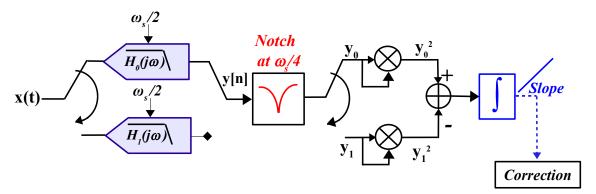

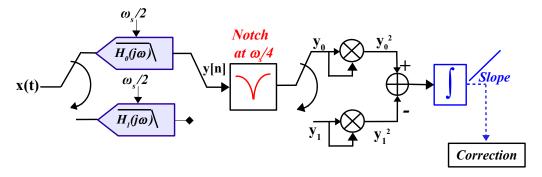

est basée sur l'estimation de l'erreur de gain entre les deux voies constituant le convertisseur TIADC. Dans un premier temps, nous avion considéré des toutes les autres erreurs (offset, gain et skew) préalablement compensée et nous verrons par la suite l'impact de ces erreurs sur la solution proposée. L'architecture est décrite dans la Figure. 13 où la différence des deux puissances  $y_0^2$  et  $y_1^2$  représentant la fonction de coût (fonction d'erreur) est nulle lorsque les deux convertisseurs ne présentent pas d'erreur de bande passante. Sous l'hypothèse d'un premier ordre et pour un signal sinusoidal à l'entrée, cette fonction s'exprime par :

$$loss[k] = y_0^2[k] - y_1^2[k]$$

$$= \frac{1}{2} \left\{ \frac{1}{1 + (\omega \tau_0)^2} - \frac{1}{1 + (\omega \tau_1)^2} \right\}$$

$$+ \frac{1}{2(1 + (\omega \tau_0)^2)} \cos[2\omega T(kM + 0) - 2\arctan(\omega \tau_0)]$$

$$- \frac{1}{2(1 + (\omega \tau_1)^2)} \cos[2\omega T(kM + 1) - 2\arctan(\omega \tau_1)].$$

(5)

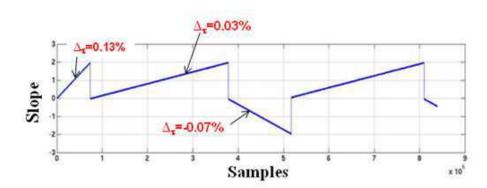

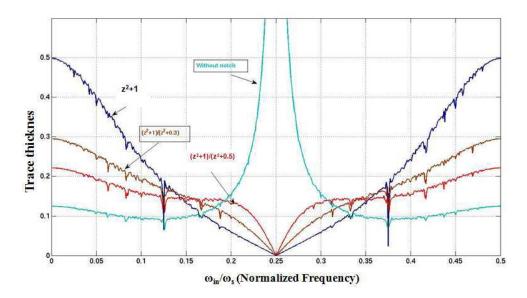

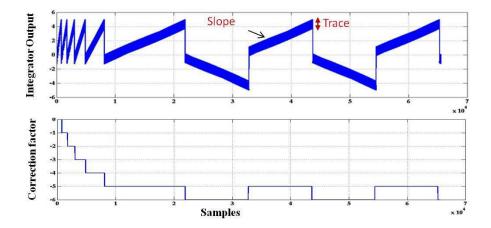

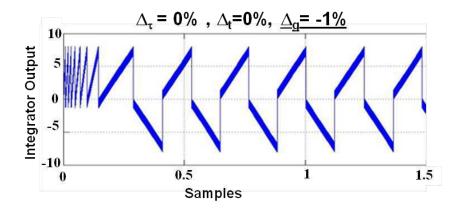

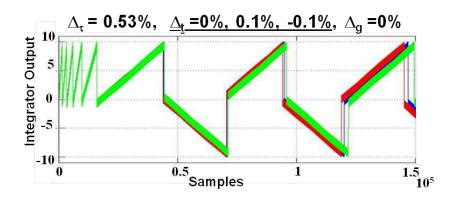

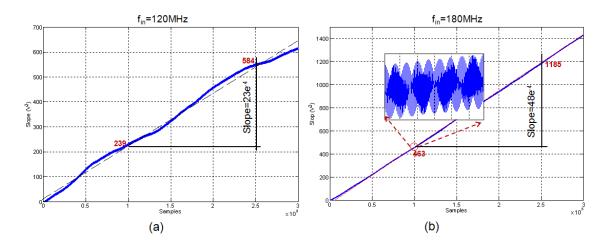

Qui peut être vue comme un signal DC + une fonction de moyenne nulle. Cette fonction d'erreur, une fois intégrée (sortie de l'intégrateur), va permettre d'extraire le DC qui comporte l'information de l'erreur de bande passante. En effet, à la sortie de l'intégrateur, la pente (notée Slope sur la figure) le représentant s'exprime par :

$$Slope = \frac{1}{2(1 + (\omega \tau_0)^2)} - \frac{1}{2(1 + (\omega \tau_1)^2)}$$

(6)

Autour de cette pente, le bruit intégré (représenté par la trace) dépend de l'erreur de la bande passante et de la fréquence d'entrée et définit le seuil de décision pour l'intégrateur. Lorsque la sortie de l'intégrateur dépasse ce seuil, nous prenons alors la décision de corriger l'une des deux voies dans et renvoyons le résultat à l'entrée de l'intégrateur jusqu'à ce que la pente devienne nulle.

Figure 13 – Estimation de l'erreur de bande passante

Il est à noter que le but est de supprimer la raie due à l'entrelacement temporel. En conséquence pour un signal à la fréquence  $\omega_s/4$ , la raie de distorsion apparait à la même fréquence, ce qui rend son extraction impossible. D'où l'intérêt d'utiliser un filtre autour de cette fréquence afin de s'affranchir de ce problème (voir Figure. 13).

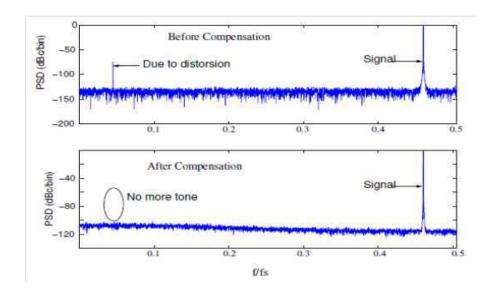

- b. Simulations et résultats

Le modèle implémentée pour l'estimation de l'erreur de bande passante a été évalué

tout d'abord par simulation puis un prototype réel a permis de valider la robustesse de la technique que nous avons proposé.

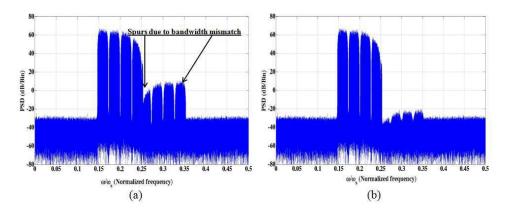

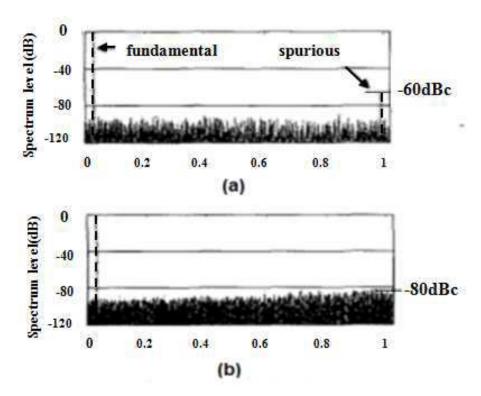

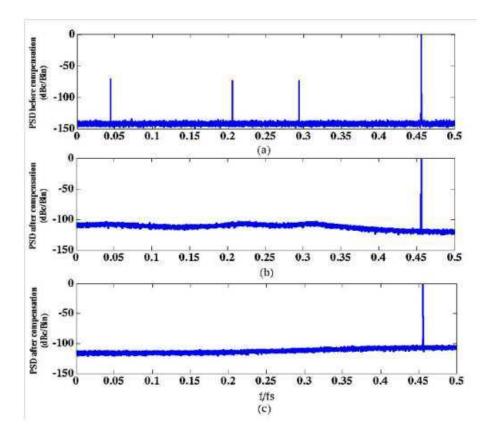

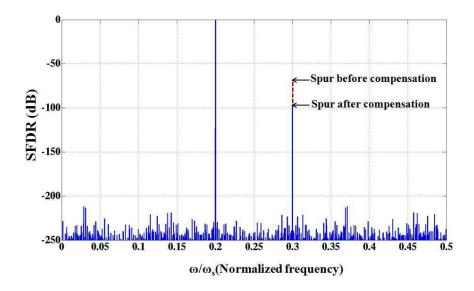

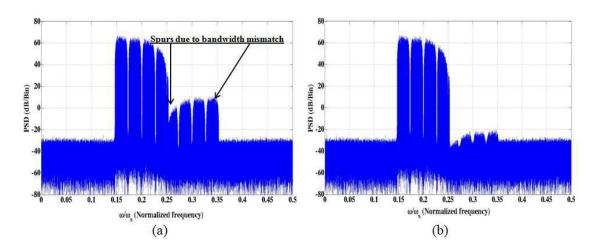

Le cas d'un signal CDMA a été traité par simulation et montre l'efficacité de cette solution. Les résultats sont représentés par la Figure. 14 où nous voyons une diminution des raies de distorsion et une amélioration du SFDR qui passe de 55 dB à 95 dB après correction analogique idéale de l'erreur extraite. Sur la Figure. 15, l'intégrateur converge après un certain temps vers la vraie valeur de l'erreur de bande (oscillation autour de zero). A noter que la figure 5.3 a est réalisée après le notch afin de voir son effet sur le signal de sortie. Cependant, la sortie utile du convertisseur se trouve avant le notch.

FIGURE 14 – Estimation de l'erreur de bande passante pour un signal CDMA.

FIGURE 15 – Sortie de l'intégrateur pour le cas d'un signal CDMA.

Par ailleurs, nous avions considéré en début de cette étude que les erreurs de gain et de skew sont préalablement corrigées. En présence de ces dernières, cette solution est limitée par la présence d'une erreur de gain statique puisque elle basée sur l'extraction des puissances des deux convertisseurs, ce qui fausserait alors l'estimation de l'erreur de la bande passante. Cependant, il est à noter que l'erreur de gain statique provient principalement de disparité entre les alimentations des deux convertisseurs et nous pallions ce problème en utilisant alors une référence commune entre les voies du TIADC. De plus, il important de noter que la solution d'estimation proposée s'affranchit du problème de skew qui plus difficile à corriger. Après avoir validé la solution par simulation, nous avons réalisé un prototype qui

à l'aide de circuit réels afin de voir ses limitations en présence d'autres sources d'erreurs.

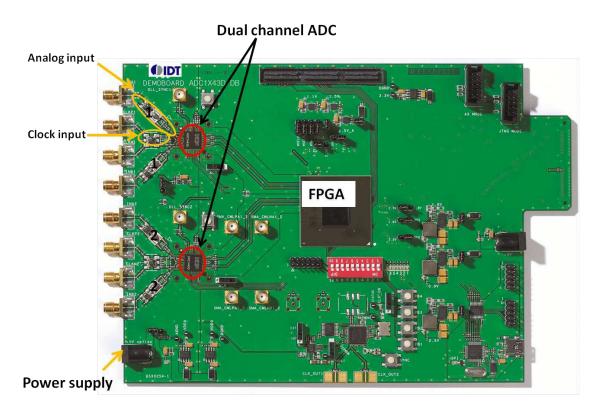

#### - c. Prototype

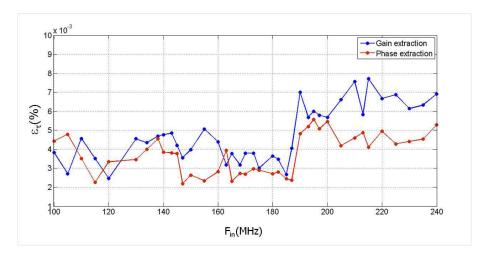

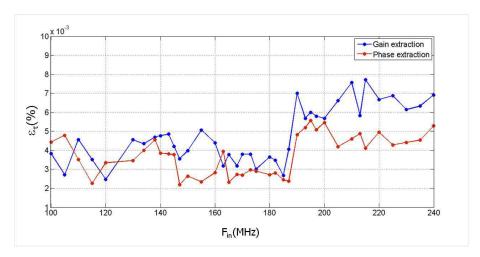

La validation de la solution proposée en utilisant des données d'un circuit en développement donne des résultats satisfaisants. Le circuit utilisé est composé de deux convertisseurs, chacun fonctionnant à 250 Msps. La première étape consiste en l'acquisition des échantillons à la sortie du convertisseur TIADC. Un post traitement est ensuite appliqué pour estimer l'erreur de la bande passante en utilisant la solution proposée. La Figure. 16 montre les résultats obtenus. La courbe en bleu représente la valeur extraite à l'aide de la solution proposée (basée sur le gain), quant à la courbe en rouge représente le calcul de l'erreur de la bande passante en se basant sur la mesure de la phase et après avoir supprimé l'erreur de skew qui peut être mesurée en basses fréquences. Comme nous pouvons le voir, la valeur extraite de la bande passante à partir de la solution proposée (courbe en bleu) varie avec la fréquence dans un intervalle [0.02%-0.05%], ce qui peut représenter une limitation pour l'extraction de l'erreur de bande pour des fréquences d'entrée très élevées. Le problème est identique pour la courbe rouge. Après une étude sur

FIGURE 16 – Estimation de l'erreur de bande passante basée sur la solution proposée (courbe en bleu) versus calcul de l'erreur de bande à l'aide la mesure de la phase (courbe en rouge)

le circuit utilisé et des mesures de bande passante, nous avons constaté que ces fluctuations dans la bande passante sont dues aux retours de charges vers le circuit d'entrée, ce qui nécessite alors une adaptation d'impédance pour isoler le circuit TIADC. Ce travail représente une perspective pour les travaux futurs.

#### IV Conclusion

Afin de réaliser un convertisseur analogique numérique à hautes performances (vitesse et linéarité) pour une application large bande station de base, l'architecture à entrelacement temporel a été choisie. Elle permet d'atteindre des vitesses importantes en parallélisant plusieurs convertisseurs qui fonctionnent à une vitesse réduite tout en ayant une maitrise sur la consommation globale du convertisseur. Cependant, cette architecture présente des

erreurs d'appariement entre les voies la constituant et qui réagissent différemment aux variations de l'environnement. Les erreurs les plus connues sont l'offset, le gain et le skew et qui sont largement traitées dans la littérature. Cependant, pour les applications larges bandes, l'erreur de la bande passante entre les voies devient visible et son impacte sur les performances en linéarité (SFDR) important. Nous avons alors montré que pour atteindre un SFDR >90dB à 380MHz d'entrée, l'erreur de bande passante doit être inférieure à 0.02%, ce qui difficile à réaliser. Très peu de travaux traitent cette erreur et nous nous somme proposés d'apporter 2 solutions pour pallier ce problème. La première consiste à réduire l'impacte de l'erreur de bande passante en randomisant les réseaux d'entrée du TIADC en ajoutant des circuits d'entrée supplémentaires. Ceci permet d'étaler les raies de distorsion sur toute la bande mais la puissance de bruit dans la bande reste constante. De ce fait, cette solution peut être utilisée en complément à d'autres solutions qui réduiraient l'erreur préalablement. Une solution d'estimation de l'erreur de bande passante a également été proposée. Elle est basée sur l'extraction de la contribution de gain. Cette solution a été validée par simulation à l'aide d'un signal large bande CDMA et un prototype de mesure a été mis en place et a permis de vérifier la robustesse de cette solution. Cependant, des réflexions dans la bande passante rendent l'extraction moins précise et de ce fait, il est important d'avoir des circuits bien adaptés avant d'utiliser des techniques d'extraction de la bande passante.

#### V Perspectives

La perspective principale à ce projet est de trouver une solution de séparation de toutes les erreurs afin d'avoir une estimation aveugle de celles-ci et permet de corriger les erreurs séparément dans le domaine analogique. Ce dernier constitue le travail le plus important. En effet, la correction analogique permet de consommer moins que la correction digitale et présente une meilleure résolution. De plus les variations de l'erreur de bande passante extraite représente un verrou technologique qu'il va falloir lever pour permettre une estimation précise. Enfin, la Figure. 17 donne une vision à moyen terme des travaux de recherche pour atteindre de meilleures performances avec des architectures à entrelacement temporel.

Figure 17 – perspectives pour les travaux futurs

#### Abstract

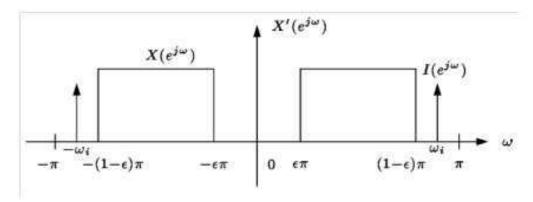

The rapid evolution of wireless communications pushes the analog-to-digital converter close to the antenna in order to address multistandard transceivers for Software Define Radio (SDR). In that case, wide band base stations require high speed, high resolution analog-to-digital converter (ADC). Time-interleaved ADC architecture (TI-ADC) is an efficient way to increase the sampling frequency. It consists of the parallelization of several channels; each one running at the overall data rate (fs) divided by the number of channels M. However, due to IC process and temperature variations, mismatches between the channels generate errors which impact the linearity of the converter and hence degrade the SFDR. Several solutions deal with the problems of offset, gain and timing skew errors, when only few works have considered the bandwidth mismatch problem. This error comes from the fact that during the sampling period, the sampling networks behave differently as low pass filters. The difference between the cutoff frequencies of the channels input filters cause bandwidth mismatch error. This error intervenes as gain and phase modulation and these two components depend on the input frequency and are nonlinear dependent of the bandwidth mismatch error. For these two reasons, background calibration is necessary. In this work, we have focused on the bandwidth mismatch error and proposed some solutions to deal with it. Two approaches have been proposed:

The first one consists of reducing the impact of the bandwidth mismatch error by randomizing the input sampling networks. In fact, mismatch error in a time-interleaved architecture is caused by a cyclic pattern and the easiest way to reduce this cyclic characteristic consists of randomizing the channels and spreading in that way the spurs over the bandwidth. A new implementation has been proposed using additional sample networks to achieve the randomization instead of entire channels. Compared to existing methods, the proposed implementation allows reducing power consumption and die area. Moreover, it is possible to compensate all errors due to switches mismatch such as timing skew error.

The second approach consists of compensating the bandwidth mismatch error using estimation and correction. We have focused on digital error estimation since it is very important to accurately extract the error. Bandwidth mismatch error is present in both ADC output gain and phase error components. A comparison between the two components has shown that the gain and phase errors due to bandwidth mismatch are comparable, consequently, the error can be estimation using either gain or phase extraction. Based on this analysis, a background estimation of the bandwidth mismatch using gain extraction has been proposed. It has the advantage to be free dependent from the clock skew mismatch but is impacted by the static gain error. This latter can be overcome either by design or using low frequencies offline compensation techniques. Nevertheless, the estimation of this static gain error can be done using the proposed solution. Moreover, thanks to this individual error estimation technique, either analog or digital correction can be applied. On the contrary, other existing solutions based on polynomial approximation address a global error including gain and skew which limits to calibration to digital correction. The proposed solution has been first validated by simulation, then robustness has been evaluated using a wide band WCDMA signal. This realistic use case has probabilistic properties avoiding the presence of two symmetrical signals at the same time. This latter configuration generates undesired spurs at the same frequencies which are not managed by the integrator for deterministic signals. Finally, the impact of measured intrinsic errors of the ADCs has been considered to validate the proposed estimation technique.

## Table des matières

| A            | bstra           | et                                                   | 2  |

|--------------|-----------------|------------------------------------------------------|----|

| Sy           | mbo             | ls and Abbreviations                                 | 9  |

| $\mathbf{R}$ | ésum            | é en français                                        | 13 |

| In           | $\mathbf{trod}$ | uction                                               | 14 |

| 1            | Hig             | h Speed High Resolution Analog-to-Digital Converters | 19 |

|              | 1.1             | Introduction                                         | 19 |

|              | 1.2             | Analog-to-Digital Converters                         | 19 |

|              |                 | 1.2.1 Ideal Converters                               | 19 |

|              |                 | 1.2.1.1 Sampler                                      | 20 |

|              |                 | 1.2.1.2 Quantization                                 | 22 |

|              | 1.3             | ADC versus Specifications                            | 24 |

|              |                 | 1.3.1 Static specifications                          | 24 |

|              |                 | 1.3.2 Offset and gain error                          | 24 |

|              |                 | 1.3.3 Nonlinearity                                   | 24 |

|              |                 | 1.3.4 Dynamic specifications                         | 25 |

|              | 1.4             | Towards High Speed ADC Architectures                 | 27 |

|              |                 | 1.4.1 Nyquist ADCs                                   | 28 |

|              |                 | 1.4.1.1 Flash converters                             | 28 |

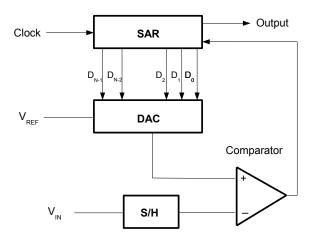

|              |                 | 1.4.1.2 SAR ADCs                                     | 28 |

|              |                 | 1.4.1.3 Pipeline ADCs                                | 30 |

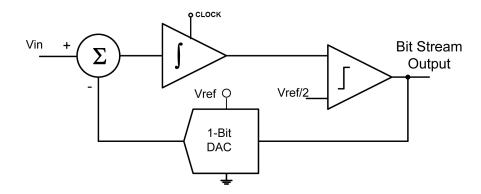

|              |                 | 1.4.2 Oversampling ADCs                              | 31 |

|              |                 | 1.4.3 Time-interleaved ADCs                          | 32 |

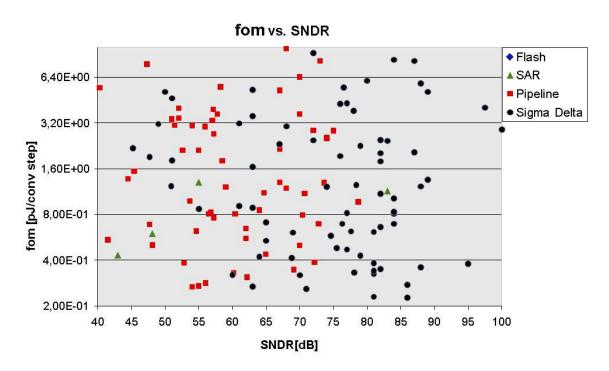

|              | 1.5             | ADC Trend                                            | 34 |

|              |                 | 1.5.1 Global Converters trend from 1999 to 2012      | 34 |

|              |                 | 1.5.2 Figure of merit                                | 36 |

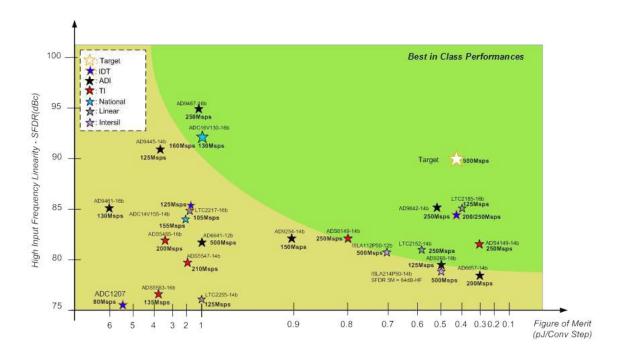

|              |                 | 1.5.3 Some outstanding architectures                 | 36 |

|              | 1.6             | Wireless base station application                    | 38 |

|              |                 | 1.6.1 ADC performance requirements                   | 38 |

|              | 1.7             | Chapter Conclusion                                   | 39 |

| 2            | Tim             | ne-Interleaved ADCs                                  | 41 |

|              | 2.1             | Introduction                                         | 41 |

|              | 2.2             | Channel modelling                                    |    |

|              | 2.3             | Impact of the mismatch errors                        | 46 |

|   |       | 2.3.1 Offset mismatch                                                                       | 46              |

|---|-------|---------------------------------------------------------------------------------------------|-----------------|

|   |       | 2.3.2 Gain mismatch                                                                         | 48              |

|   |       | 2.3.3 Clock skew mismatch                                                                   | 50              |

|   |       | 2.3.4 Bandwidth mismatch                                                                    | 52              |

|   | 2.4   | Overall Performance limitations                                                             | 56              |

|   | 2.5   | Chapter Conclusion                                                                          | 57              |

| 3 | Ban   | ndwidth Mismatch Error Calibration                                                          | <b>5</b> 9      |

|   | 3.1   | Random Sampling Technique                                                                   | 59              |

|   |       | 3.1.1 Literature review                                                                     | 60              |

|   |       | 3.1.2 The proposed randomization technique using additional samplers                        | 62              |

|   |       | 3.1.2.1 Concept                                                                             | 62              |

|   |       | 3.1.2.2 Impact of the number of additional samplers                                         | 63              |

|   | 9.0   | 3.1.3 conclusion                                                                            | 66              |

|   | 3.2   | Bandwidth Mismatch Calibration Techniques                                                   | 66              |

|   |       | 3.2.1 Introduction                                                                          | $\frac{66}{67}$ |

|   |       | 3.2.2 Background calibration techniques                                                     | 67              |

|   |       | 3.2.2.1 Correction techniques                                                               | 72              |

|   |       | 3.2.3 Conclusion                                                                            | 79              |

|   | 3.3   | Chapter conclusion                                                                          |                 |

|   | 0.0   | Chapter conclusion                                                                          | 01              |

| 4 |       | posed Detection Technique: Bandwidth Mismatch Estimation                                    | 83              |

|   | 4.1   | Introduction                                                                                |                 |

|   | 4.2   | Proposed Technique Overview                                                                 | 83              |

|   |       | 4.2.1 Proposed extraction technique                                                         |                 |

|   |       | 4.2.1.1 System model                                                                        | 90              |

|   |       | 4.2.1.2 Simulation and validation 4.2.2 Static gain and clock skew impact on the extraction | $90 \\ 92$      |

|   |       | 4.2.3 Conclusion                                                                            | 93              |

|   | 4.3   | Prototype                                                                                   |                 |

|   | 1.0   | 4.3.1 Introduction                                                                          | 94              |

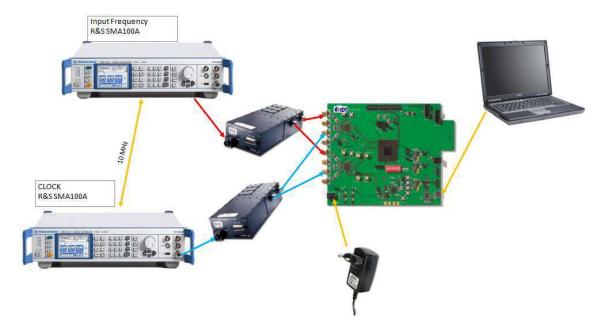

|   |       | 4.3.2 Board description and test setup                                                      |                 |

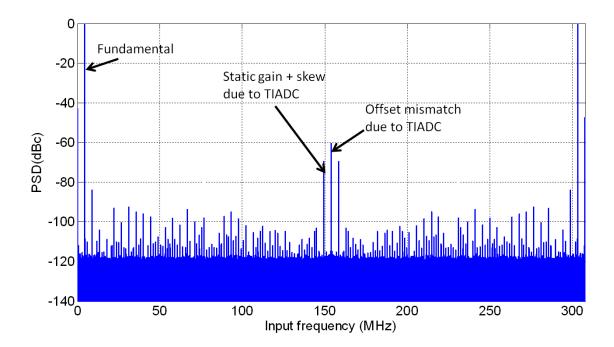

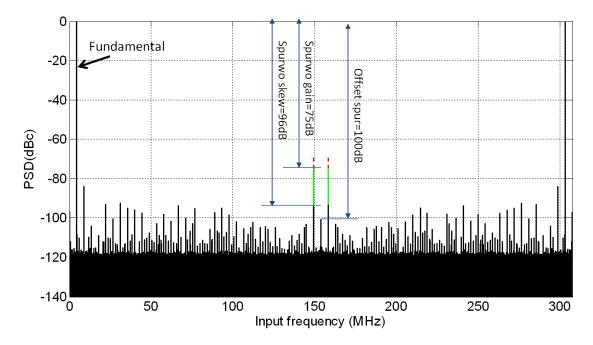

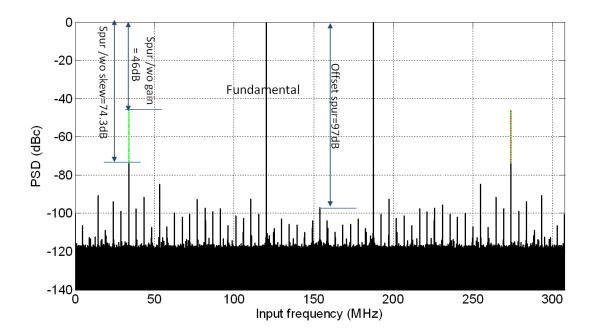

|   |       | 4.3.3 Measurements results                                                                  |                 |

|   | 4.4   | Chapter conclusion                                                                          |                 |

| _ |       | •                                                                                           |                 |

| C | onclu | ision                                                                                       | 101             |

| A | ppen  | dix A: Bandwidth mismatch simulation                                                        | 105             |

| B | bliog | graphy                                                                                      | 118             |

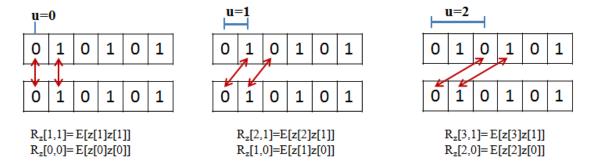

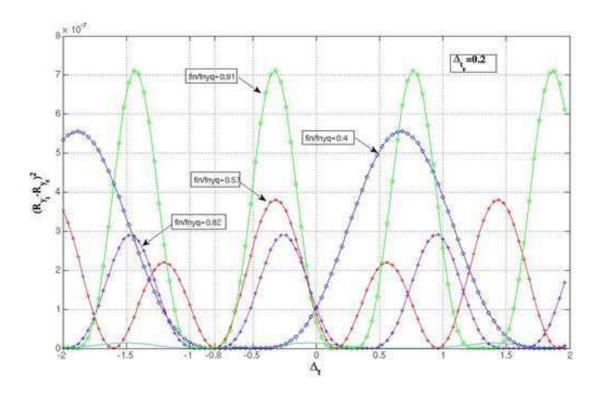

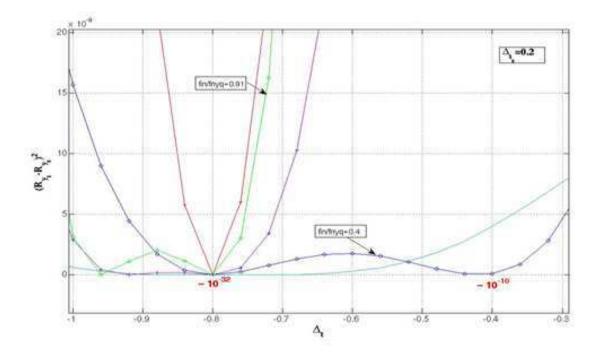

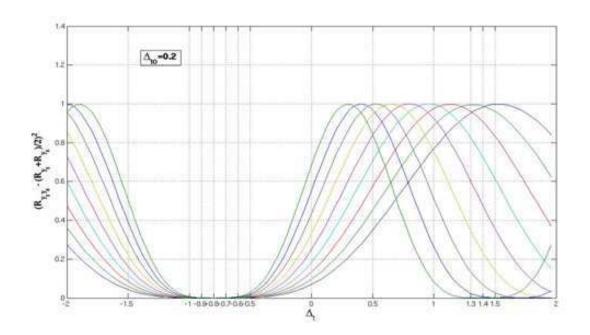

## List of Figures

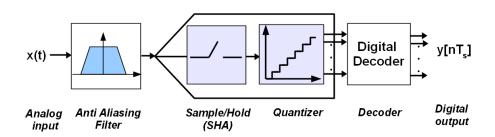

| 1.1  | Analog-to-digital converter blocks : anti-aliazing filter, sampling block, quan-    |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | tizer and decoder blocks                                                            | 20  |

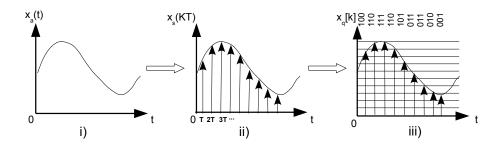

| 1.2  | (i) Analog signal, (ii) Sampled signal, (iii) Quantized signal                      | 20  |

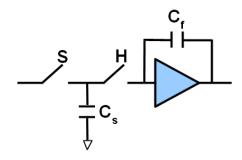

| 1.3  | Sample and Hold circuit                                                             | 21  |

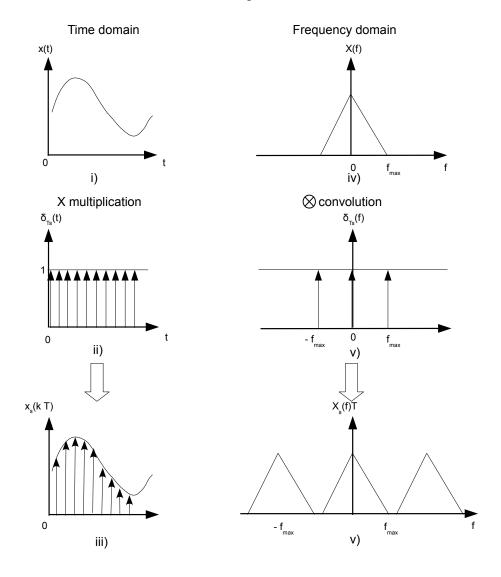

| 1.4  | sampling signal in time and frequency domains                                       | 21  |

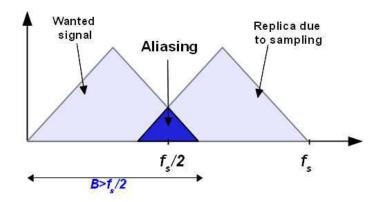

| 1.5  | Aliasing from the adjacent spectral band                                            | 22  |

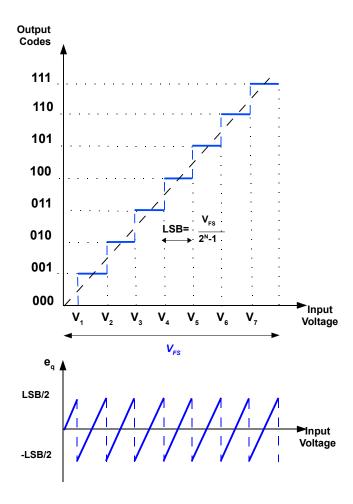

| 1.6  | (a) Quantizer In/Out characteristic and (b) quantization error                      | 23  |

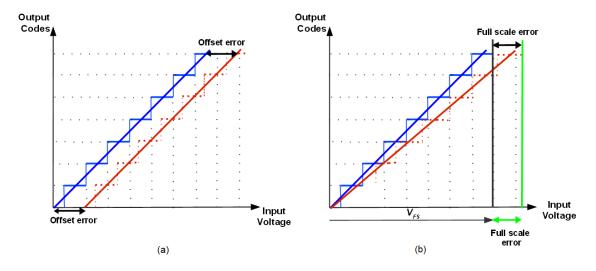

| 1.7  | (a) Offset Error, (b) Gain Error                                                    | 24  |

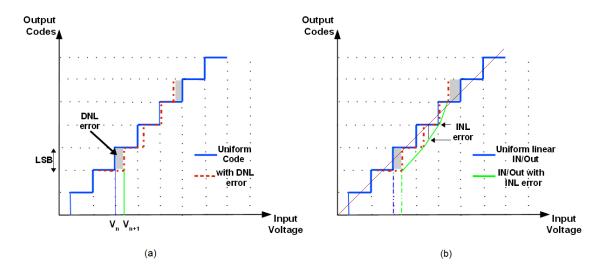

| 1.8  | (a) Differential nonlinearity (DNL) (b) Integral nonlinearity (INL)                 | 25  |

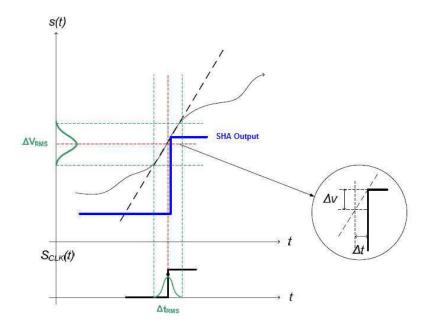

| 1.9  | Jitter effect                                                                       | 26  |

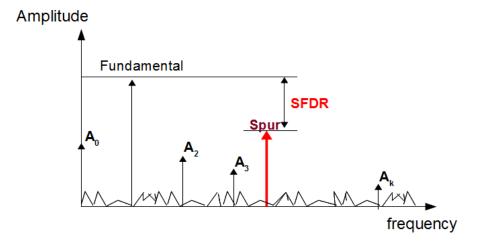

| 1.10 | Dynamic specifications at the output spectrum                                       | 27  |

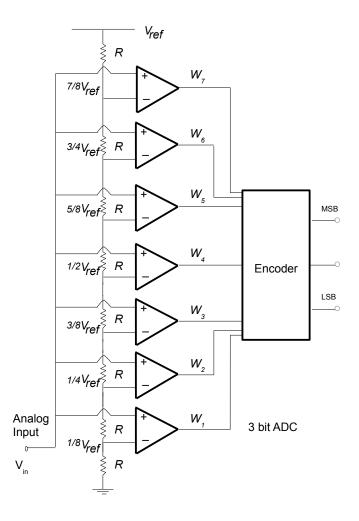

| 1.11 | A 3-bits flash ADC.                                                                 | 29  |

| 1.12 | Successive Approximation architecture                                               | 30  |

| 1.13 | Typical 10-bit (1.5-bit per stage) Pipeline ADC architecture                        | 31  |

| 1.14 | First order $\Sigma\Delta$ modulator                                                | 32  |

| 1.15 | Time-interleaved analog to digital converter                                        | 33  |

| 1.16 | State of the Art of high performance ADCs from 1999 to 2012                         | 34  |

| 1.17 | State of the Art of high performance ADCs from 1999 to 2012 : Comparison            |     |

|      | Parallel architectures to Single channel ADCs                                       | 36  |

| 1.18 | ADCs performance in terms of the Factor of Merit and resolution                     | 37  |

|      | ADC position in a base station transceiver                                          | 38  |

| 1.20 | Comparison of our targeted ADC with the existing competitor ADCs in                 |     |

|      | terms of SFDR versus FoM                                                            | 40  |

| 0.1  | M. I I I. A. D. C I I. I                                 | 40  |

| 2.1  | M-channels time-interleaved ADC and sampling phase                                  | 42  |

| 2.2  | <i>i</i> -th channel including distortion errors : offset, gain, skew and bandwidth | 40  |

| 0.0  | mismatch.                                                                           | 43  |

| 2.3  | Time-interleaved converter including all distortion errors : offset, gain, skew     | 40  |

| 0.4  | and bandwidth mismatch.                                                             | 43  |

| 2.4  | Output spectrum including mismatch errors : offset, gain, skew and band-            | 1.0 |

| ٥٢   | width for a 2 and 4 channels ADC                                                    | 46  |

| 2.5  | Offset error impact on the 2 channels TI-ADC output in (a) time domain              | 4 7 |

| 0.0  | and (b) frequency domain.                                                           | 47  |

| 2.6  | Gain error mismatch on the output in time and frequency domain                      | 49  |

| 2.7  | SFDR versus gain mismatch error                                                     | 49  |

| 2.8  | Gain distribution of the two channels imposed by references' variations             | 50  |

| 2.9  | SFDR Performance versus skew error                                                  | 51  |

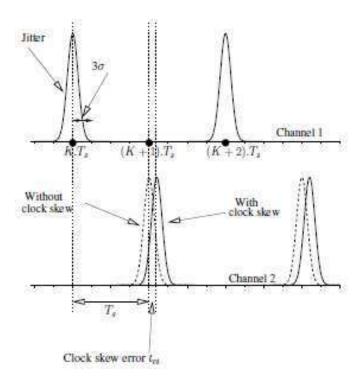

| 2.10 | Clock skew error on the output in time and frequency domain                         | 52  |

6

| 2.11 | SFDR Performance versus skew error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 53  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

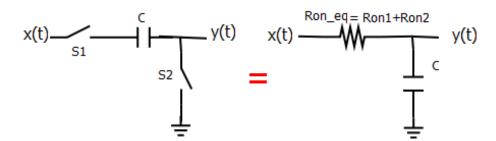

| 2.12 | Sampling network and its equivalent low pass filter when the switches are $On$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 53  |

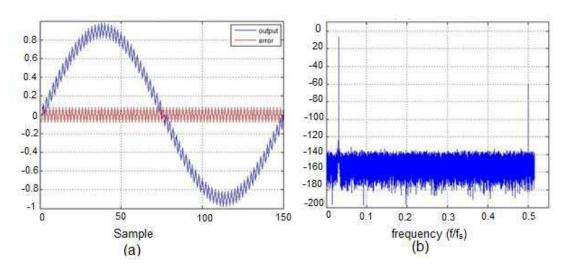

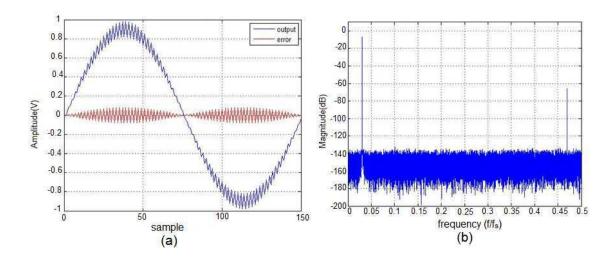

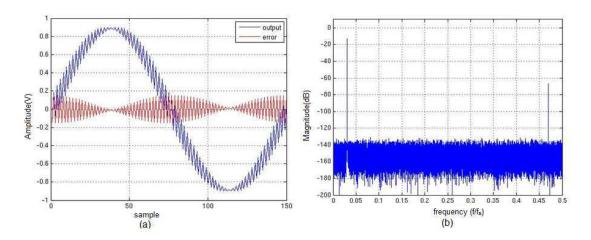

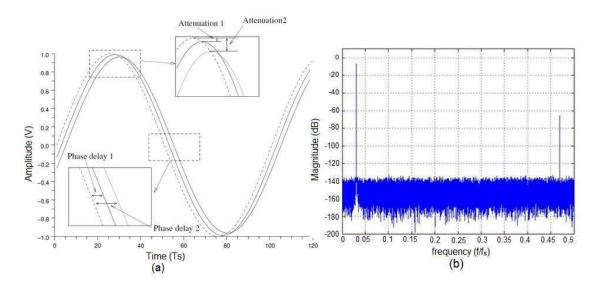

| 2.13 | Impact of the bandwidth mismatch error on the output in time and fre-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|      | quency domains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 55  |

| 2.14 | SFDR Performance versus bandwidth mismatch error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 55  |

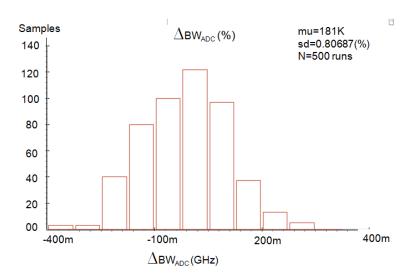

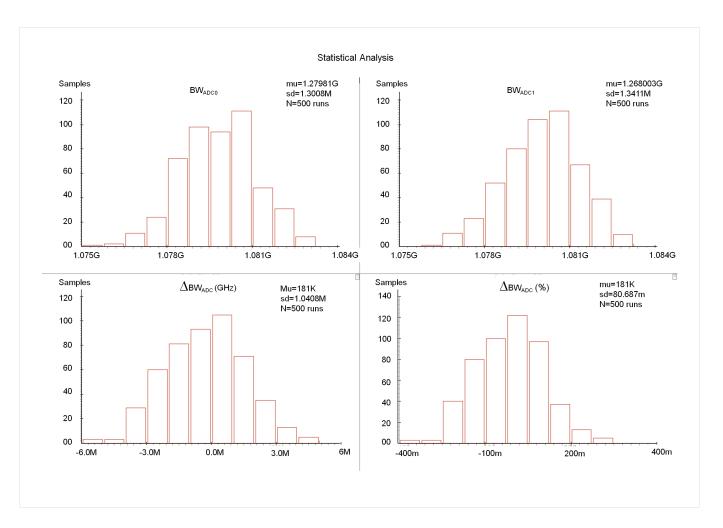

|      | Simulated Bandwidth distributions and mismatch quantification between                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|      | two channels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 56  |

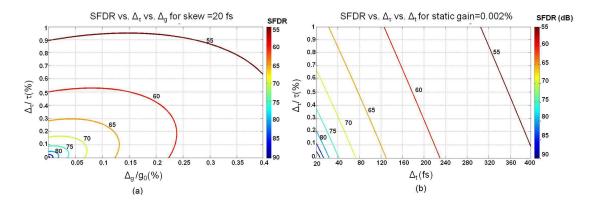

| 2.16 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|      | gain errors (b) different skew errors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57  |

| 2 17 | SFDR Performance versus bandwidth mismatch error for a gain error=0.002%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|      | and a skew error = $20$ fs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 58  |

|      | and a show circle 2015 in the circle and a show circle 2015 in the circle and a show |     |

| 3.1  | Channel random sequence. (a) without additional ADC (M=3, R=0), (b) with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | c c |

| 2.0  | additional channel (M=2, R=1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 60  |

| 3.2  | TI-ADC with M=2, R=1, (a) before randomization, (b) after randomization.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.1 |