## Multi-electrode system design and optimization for cardiac implants

Islam Seoudi

## ► To cite this version:

Islam Seoudi. Multi-electrode system design and optimization for cardiac implants. Other. Télécom ParisTech, 2012. English. NNT: 2012ENST0027 . tel-01081680

## HAL Id: tel-01081680 https://pastel.hal.science/tel-01081680

Submitted on 10 Nov 2014  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

2012-ENST-027

## **Doctorat ParisTech**

# THÈSE

Pour obtenir le grade de docteur délivré par

## Télécom ParisTech

## Spécialité "Electronique et Communications"

Présenté et soutenue publiquement par

## Islam SEOUDI

5 juin 2012

## **Multi-electrode System Design and Optimization for Cardiac Implants**

Directeur de thèse : Amara AMARA

| Jury                                                                              |                       | - |

|-----------------------------------------------------------------------------------|-----------------------|---|

| M. Marc Belleville, Chief Scientist, CEA-Leti                                     | RAPPORTEUR            |   |

| M. Jean-Michel PORTAL, Professeur, Ecole Polytechnique Universitaire de Marseille | RAPPORTEUR            | н |

| M. Christian PIGUET, Professeur, CSEM                                             | EXAMINATEUR           |   |

| Mme Lirida NAVINER, Professeur, Telecom ParisTech                                 | EXAMINATEUR           | È |

| M. Alain RIPART, Vice-President, Sorin CRM                                        | EXAMINATEUR           |   |

| M. Daniel KROISS, Vice-President & Chief Scientific Officer, Sorin CRM            | INVITE                | S |

| M. Amara AMARA, Directeur de Recherche, ISEP                                      | DIRECTEUR DE THESE    | U |

| Mme Karima AMARA, Ingénieur Project, Sorin CRM                                    | CO-DIRECTEUR DE THESE | Е |

Télécom ParisTech Grande école de l'Institut Télécom – membre fondateur de ParisTech 46, rue Barrault – 75634 Paris Cedex 13 – Tél. + 33 (0)1 45 81 77 77 – www.telecom-paristech.fr

# Title: Multi-Electrode System Design and Optimization for Cardiac Implants

Abstract: Cardiac implants like ICD (Implantable Cardioverter Defibrillator) are life saving devices in cases of sudden cardiac arrhythmias. In other conditions like the one of heart failure, cardiac implants like CRT (Cardiac Rhythm Therapy) are prescribed to restore the coordinated contraction of the heart. Such treatment consists of the delivery of localized electrical stimuli to the cardiac tissue via electrodes in the stimulation lead. Conventionally the stimulation lead come either in unipolar or bipolar configuration (1 or 2 electrode) which have been found to be sufficient for pacing the right atrium and right ventricle, studies have shown the benefits of a multi-electrode system for pacing left ventricle essential for cardiac resynchronization. This thesis discusses the design and optimization of a multi-electrode system capable of alleviating the limitations and constraints related to left ventricular stimulation. We first present a chip implementation of such multi-electrode system. It was taped out in 0.18 µm technology and occupies 2.25x5.35 mm<sup>2</sup> area . The chip also features a specially designed communication protocol and is compliant with the existing standards. It enables low power operation and allows quick configuration. Thereafter we present the design and implementation of a default connection unit (DCU) to ensure the compatibility of our multi-electrode lead with pacemakers not designed specifically to control such a lead. Like the multi-electrode chip the DCU unit was taped out in 0.18 µm technology, occupies 2.2 x 1.75 mm<sup>2</sup> area and harvests the stimulation energy to power itself. Finally we present a proof of concept study for the adaptation and integration of non-volatile memory technologies within the multi-electrode system. New technologies were explored which drastically improve the performance of the multi-electrode system. The employment of such technologies enhanced our multi-electrode system by eliminating the need of repetitive configuration of electrodes, thereby saving power and reducing latency. The benefits also included smaller area and compatibility with any pacemaker in the market. Through simulations we proved the feasibility of these technologies for our implant applications.

Keywords : Cardiac pacemakers, multi-electrode, stimulation, medical implants, switching, MOS, non-volatile, memories

## Titre : Conception et Optimisation de Système Multi-électrodes Pour Les Implants Cardiaques

Résumé: Les implants cardiaques tels que les défibrillateurs implantables sont des appareils permettant de sauver la vie dans le cas de troubles de l'arythmie cardiaque soudaine. Tandis que dans le cas des attaques cardiaques, les implants CRT sont utilisés pour rétablir la cadence de la contraction cardiaque. De tels traitements consistent en l'application de stimulations locales au tissue cardiaque via des électrodes se trouvant dans les sondes de stimulation. Ces dernières se présentent soit dans une configuration unipolaire ou bipolaire ; qui ont prouvé leur efficacité pour stimuler le ventricule droit et l'oreillette droite ; des études ont montré l'efficacité de la sonde multiélectrode dans la stimulation du ventricule gauche indispensable pour la resynchronisation cardiaque. Cette thèse traite de la conception et l'optimisation d'un système multi-électrodes capable d'éviter les limitations et les contraintes liées à la stimulation du ventricule gauche. Tout d'abord, une réalisation de ce système cette est présentée et fabriqué dans une technologie 0.18 µm. Le circuit a également un protocole de communication spécifique. Il permet une opération basse consommation et une configuration rapide. Ensuite, la conception et la réalisation d'une unité de configuration par default est présentée. Cette unité assure la compatibilité de notre sonde avec les stimulateurs cardiaques du marché. Finalement, une étude pour l'adaptation et l'intégration des technologies mémoire non-volatile dans la sonde est présentée. De telles technologies améliorent considérablement le système en évitant le besoin de reconfiguration des sondes et en conséquence réduire la latence et la consommation.

**Mots clés:** implants cardiaques, pacemaker, multi-électrodes, sondes, switching, MOS, mémoires non volatile

# Acknowledgment

I would like to thank Mr. Renzo Dal Molin for this exceptional opportunity to work with him at the Advanced Research Department of Sorin Group from where this thesis work started. I would like to thank Professor Amara for accepting me as his student for which I'm grateful. I was lucky enough to have Professor Amara as my PhD director. He gave the example how an advisor can be as a father for his student, offers him unlimited support without counting, and lighting the dark paths full of doubts and unclear ideas.

I am grateful to Karima Amara for revealing all the secrets of digital electronics design for me. She also taught me how to insist and dig after the promising ideas and to be equipped with patience in order to convert them into meaningful inventions. I am also grateful to Jean-Francois Debroux and Marc Laflutte for revealing all the secrets of analog electronics design for me and for their unquestionable support and sincere advice.

I will strongly remember Alaa Makdissi with his rich scientific discussions and his enormous capacity to retrieve solutions for persistent problems. I want to thank him for his sincere advice and support.

All my thanks and gratitude I would present them to my friend Ashutosh who gave a perfect example for how a friend can support sincerely and generously his friend. When talking about generosity, I cannot forget Balwant Godara for being so kind, helpful and generous in giving me advice.

I would like to thank all my colleagues with whom I enjoyed to work:

Sir Julien Ardelean, Sebastien Jackard and all the "advanced research", Fabrice Gayral, Bruno Eon, Jean-Claude Bierg, Didier Gourgousse, Jean-Pierre Noel, Jean-Yves and all the R&D, Bruno, Adel, Etienne, Wen, Nabil and all V&V, Emmanuel Bigen and all System design at Sorin.

I am also grateful to Francis Chan Wai Po, Costin Anghel, Andrei Vladimirescu and wish all the best for Hraziia, Rutwick, Adam and Khaja in their Phd.

In such special moments, special persons are always remembered because without them I wouldn't have reached this achievement today. To my father Zakaria and my mother Elham I owe them this achievement and nothing can be presented to them in return other than an eternal thanks and gratitude.

To my wife Salma I present my gratitude for her support in many difficult periods of this thesis and for always pushing me forward to reach my goals.

To my brothers Yahia, Ahmed and Nour: thanks for your continuous support and for urging me constantly towards higher achievements and bigger success.

To all my Seoudi and Hammouda families I dedicate this work.

# Contents

| Acknowledgment                                                                                              | 5              |

|-------------------------------------------------------------------------------------------------------------|----------------|

| Contents                                                                                                    | 7              |

| List of Figures                                                                                             | 12             |

| List of Tables                                                                                              | 15             |

| Résumé de la thèse en Français                                                                              | 17             |

| Chapitre 1: Introduction                                                                                    | 18             |

| Chapitre 2: Les Implants de Stimulation Cardiaque                                                           | 21             |

| Système de stimulation cardiaque implantable                                                                | 22             |

| Thérapie de resynchronisation cardiaque (CRT)                                                               | 23             |

| Chapitre 3: Système Multi-Electrodes Pour La Stimulation Ventriculaire Gauche: Concep<br>Mise en Œuvre      | otion et<br>25 |

| Système Multi-Electrode : Principe & Contraintes                                                            | 25             |

| Conception et implémentation du système                                                                     | 26             |

| Résultat de Mesure                                                                                          | 31             |

| Chapitre 4: Unité de Connexion Par Défaut                                                                   | 32             |

| Les choix et défies de conception                                                                           | 33             |

| Le Principe de l'opération du DCU                                                                           | 34             |

| Résultats                                                                                                   | 35             |

| Chapitre 5 : L'Amélioration de la Sonde Multi-Electrode en Utilisant La Technolog<br>Mémoires Non-Volatiles | gie des<br>35  |

| 1 Chapter 1                                                                                                 | 40             |

| 2 Chapter 2                                                                                                 | 44             |

| 2.1 Introduction                                                                                            | 46             |

| 2.2 Human Heart and Cardiac Implant Evolution                                                               | 46             |

| 2.2.1 Heart failure condition                                                                               | 48             |

| 2.2.2 Arrhythmias                                                                                           | 48             |

| 2.2.3 First Implantable pacemaker                                                                           | 48             |

| 2.2.4 Demand Pacemaker                                                                                      | 49             |

| 2.2.5 Rate-Responsive Pacemaker                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 49                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.3 Implantable Cardiac Stimulation System                                                                                                                                                                                                                                                                                                                                                                                                                                        | 49                                                                                                                                                                     |

| 2.3.1 Pulse Generator (Implant - CAN)                                                                                                                                                                                                                                                                                                                                                                                                                                             | 51                                                                                                                                                                     |

| 2.3.1.1 Power source                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 51                                                                                                                                                                     |

| 2.3.1.2 Output circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 52                                                                                                                                                                     |

| 2.3.1.3 Sensing Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 56                                                                                                                                                                     |

| 2.3.1.4 Control unit                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 58                                                                                                                                                                     |

| 2.3.2 Leads                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 59                                                                                                                                                                     |

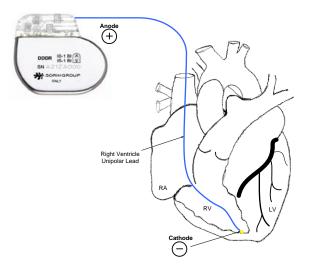

| 2.3.2.1 Unipolar                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 60                                                                                                                                                                     |

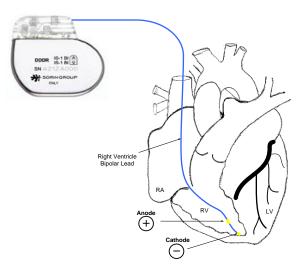

| 2.3.2.2 Bipolar                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60                                                                                                                                                                     |

| 2.4 Cardiac Resynchronization Therapy (CRT)                                                                                                                                                                                                                                                                                                                                                                                                                                       | 61                                                                                                                                                                     |

| 2.4.1 Phrenic nerve stimulation                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 62                                                                                                                                                                     |

| 2.4.2 Limited choice of stimulation site                                                                                                                                                                                                                                                                                                                                                                                                                                          | 62                                                                                                                                                                     |

| 2.4.3 Lead displacement                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 62                                                                                                                                                                     |

| 2.5 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 63                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                        |

| References                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 64                                                                                                                                                                     |

| References 3 Chapter 3                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 64<br><b>66</b>                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                        |

| 3 Chapter 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 66                                                                                                                                                                     |

| 3 Chapter 3<br>3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>66</b><br>68                                                                                                                                                        |

| <ul> <li>3 Chapter 3</li> <li>3.1 Introduction</li> <li>3.2 Multi-electrode System: Principle &amp; Constraints</li> </ul>                                                                                                                                                                                                                                                                                                                                                        | <b>66</b><br>68<br>69                                                                                                                                                  |

| <ul> <li>3 Chapter 3</li> <li>3.1 Introduction</li> <li>3.2 Multi-electrode System: Principle &amp; Constraints</li> <li>3.1.1 Compliance with standards</li> </ul>                                                                                                                                                                                                                                                                                                               | <b>66</b><br>68<br>69<br>70                                                                                                                                            |

| <ul> <li>3 Chapter 3</li> <li>3.1 Introduction</li> <li>3.2 Multi-electrode System: Principle &amp; Constraints</li> <li>3.1.1 Compliance with standards</li> <li>3.1.2 Communication protocol: Power and Configuration</li> </ul>                                                                                                                                                                                                                                                | <b>66</b><br>68<br>69<br>70<br>71                                                                                                                                      |

| <ul> <li>3 Chapter 3</li> <li>3.1 Introduction</li> <li>3.2 Multi-electrode System: Principle &amp; Constraints</li> <li>3.1.1 Compliance with standards</li> <li>3.1.2 Communication protocol: Power and Configuration</li> <li>3.3 State of the Art</li> </ul>                                                                                                                                                                                                                  | <ul> <li>66</li> <li>68</li> <li>69</li> <li>70</li> <li>71</li> <li>71</li> </ul>                                                                                     |

| <ul> <li>3 Chapter 3</li> <li>3.1 Introduction</li> <li>3.2 Multi-electrode System: Principle &amp; Constraints</li> <li>3.1.1 Compliance with standards</li> <li>3.1.2 Communication protocol: Power and Configuration</li> <li>3.3 State of the Art</li> <li>3.3.1 Implementation Strategies for LEC</li> </ul>                                                                                                                                                                 | <ul> <li>66</li> <li>68</li> <li>69</li> <li>70</li> <li>71</li> <li>71</li> <li>71</li> <li>72</li> </ul>                                                             |

| <ul> <li>3.1 Introduction</li> <li>3.2 Multi-electrode System: Principle &amp; Constraints</li> <li>3.1.1 Compliance with standards</li> <li>3.1.2 Communication protocol: Power and Configuration</li> <li>3.3 State of the Art</li> <li>3.3.1 Implementation Strategies for LEC</li> <li>3.3.1.1 Centralized Structure</li> </ul>                                                                                                                                               | <ul> <li>66</li> <li>68</li> <li>69</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> <li>72</li> <li>72</li> </ul>                                                 |

| <ul> <li>S. Chapter 3</li> <li>3.1 Introduction</li> <li>3.2 Multi-electrode System: Principle &amp; Constraints</li> <li>3.1.1 Compliance with standards</li> <li>3.1.2 Communication protocol: Power and Configuration</li> <li>3.3 State of the Art</li> <li>3.3.1 Implementation Strategies for LEC</li> <li>3.3.1.1 Centralized Structure</li> <li>3.3.1.2 Distributed Structure</li> </ul>                                                                                  | <ul> <li>66</li> <li>68</li> <li>69</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> <li>72</li> <li>72</li> <li>73</li> </ul>                                     |

| <ul> <li>S.1 Introduction</li> <li>3.2 Multi-electrode System: Principle &amp; Constraints</li> <li>3.1.1 Compliance with standards</li> <li>3.1.2 Communication protocol: Power and Configuration</li> <li>3.3 State of the Art</li> <li>3.3.1 Implementation Strategies for LEC</li> <li>3.3.1.1 Centralized Structure</li> <li>3.3.1.2 Distributed Structure</li> <li>3.3.1.3 Direct Structure</li> </ul>                                                                      | <ul> <li>66</li> <li>68</li> <li>69</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> <li>72</li> <li>72</li> <li>73</li> <li>74</li> </ul>                         |

| <ul> <li>3 Chapter 3</li> <li>3.1 Introduction</li> <li>3.2 Multi-electrode System: Principle &amp; Constraints</li> <li>3.1.1 Compliance with standards</li> <li>3.1.2 Communication protocol: Power and Configuration</li> <li>3.3 State of the Art</li> <li>3.3.1 Implementation Strategies for LEC</li> <li>3.3.1.1 Centralized Structure</li> <li>3.3.1.2 Distributed Structure</li> <li>3.3.1.3 Direct Structure</li> <li>3.4 System Design &amp; Implementation</li> </ul> | <ul> <li>66</li> <li>68</li> <li>69</li> <li>70</li> <li>71</li> <li>71</li> <li>71</li> <li>72</li> <li>72</li> <li>72</li> <li>73</li> <li>74</li> <li>74</li> </ul> |

| 3.4.2.2 Control Unit               | 78  |

|------------------------------------|-----|

| 3.4.2.3 Oscillators                | 78  |

| 3.4.2.4 OTP Memory                 | 79  |

| 3.4.2.5 Main Switching Unit        | 79  |

| 3.4.2.6 Auxiliary Switching Unit   | 79  |

| 3.4.2.7 Charge Pump                | 80  |

| 3.4.3 Communication Protocol       | 80  |

| 3.4.3.1 Power pulses               | 83  |

| 3.4.3.2 Event Synchronization bits | 83  |

| 3.4.3.3 Configuration bits         | 83  |

| 3.4.3.4 Double Stimulation         | 87  |

| 3.4.4 Comparison                   | 88  |

| 3.5 Distributed Structure          | 88  |

| 3.6 Measurement Results            | 89  |

| 3.7 Conclusion                     | 92  |

| Publications                       | 93  |

| References                         | 93  |

| 4 Chapter 4                        | 95  |

| 4.1 Introduction                   | 97  |

| 4.2 Design Challenges and Choices  | 98  |

| 4.3 DCU Operation Principle        | 100 |

| 4.4 System Implementation          | 100 |

| 4.4.1 Architecture                 | 100 |

| 4.4.2 MOS Sizing                   | 105 |

| 4.4.3 Gate capacitance sizing      | 106 |

| 4.4.4 Noise                        | 107 |

| 4.5 Results                        | 107 |

| 4.6 Conclusion                     | 110 |

| Publications                       | 111 |

| References                         | 111 |

## 5 Chapter 5

| 5 Chapter 5                                                            | 113 |

|------------------------------------------------------------------------|-----|

| 5.1 Introduction                                                       | 115 |

| 5.2 Enhancements to the Multi-Electrode                                | 115 |

| 5.3 Advanced Non-Volatile Memory Technologies                          | 117 |

| 5.3.1 Nanotube RAM (NRAM)                                              | 117 |

| 5.3.1.1 NRAM Application for Multi-Electrode Switching Unit            | 120 |

| 5.3.2 Resistive RAM family                                             | 122 |

| 5.3.1.1 Magnetic Tunnel Junction (MTJ)                                 | 122 |

| 5.3.1.2 Memristance                                                    | 128 |

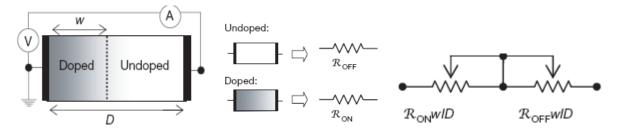

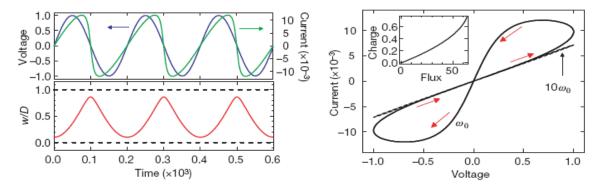

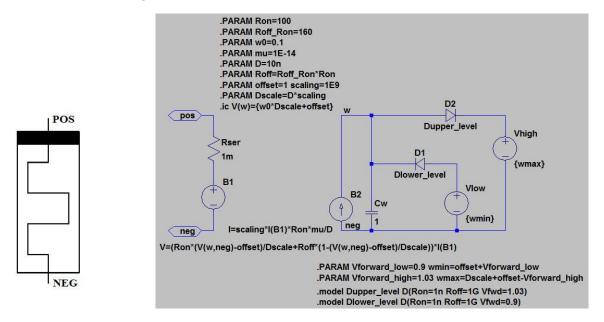

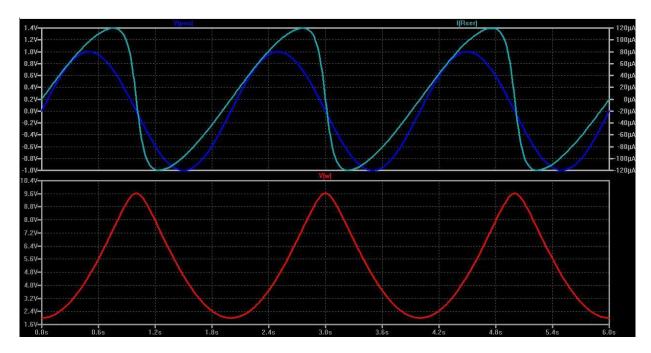

| 5.3.1.3 Memristance Behabioral Model                                   | 130 |

| 5.3.1.4 Adapting Memristance Cell for Cardiac Stimulation applications | 132 |

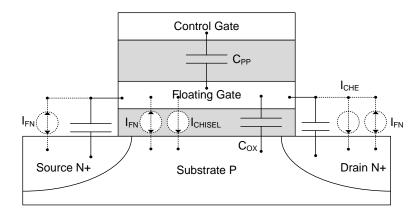

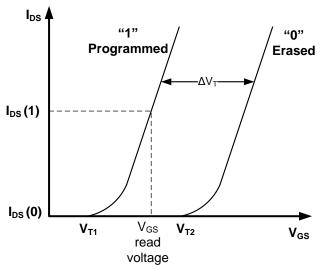

| 5.2 Conventional Non-Volatile Memory Technology: Flash Memory          | 137 |

| 5.2.1 Theoretical background                                           | 137 |

| 5.2.2 Flash cell model                                                 | 139 |

| 5.2.2.1 Program Sequence using Channel Hot Electron Method             | 139 |

| 5.2.2.2 ERASE Sequence using Fowler Nordheim Injection method          | 141 |

| 5.2.2.3 Observed Characteristics of the Flash Cell                     | 142 |

| 5.2.2.4 Operation Window expansion to adapt with our application       | 142 |

| 5.2.2.5 Evolution of VT with QFG0 (simulation)                         | 143 |

| 5.2.3 Non-Volatile Switching Unit Using Flash Memory Cell              | 144 |

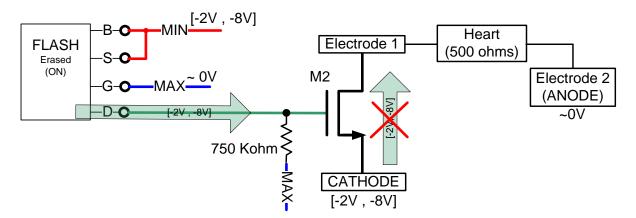

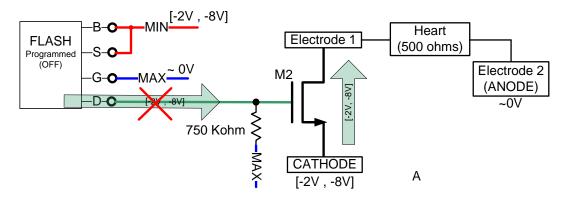

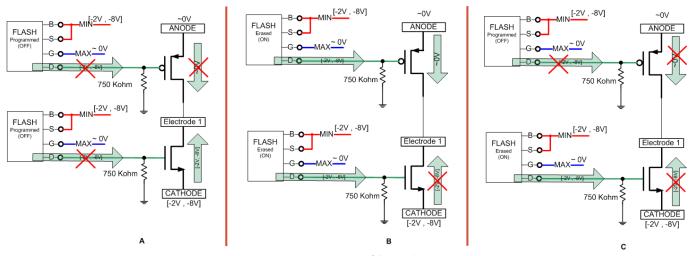

| 4.3.1 Case 1: MOS Switch connects Cathode to Electrode                 | 146 |

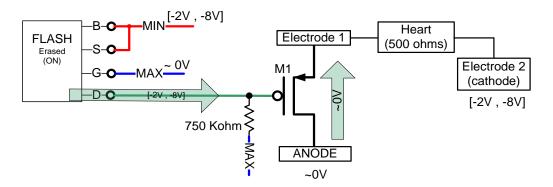

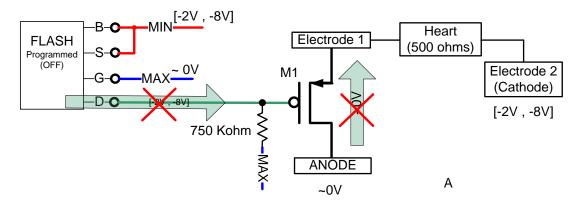

| Case 2: MOS Switch connects Anode to Electrode                         | 148 |

| 5.2.4 Summary                                                          | 151 |

| 5.3 Conclusion                                                         | 153 |

| Publications                                                           | 153 |

| References                                                             | 154 |

| 6 Chapter 6                                                            | 157 |

| List of Publications                                                   | 161 |

# **List of Figures**

| Figure 0-1: système de conduction du cœur                                                     |      |

|-----------------------------------------------------------------------------------------------|------|

| Figure 0-2: (a) défibrillateur Implantable (b) Pacemaker Implantable                          | . 22 |

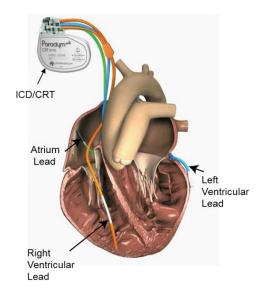

| Figure 0-3: CRT pacemaker avec trios sondes de stimulation connectés au cœur                  | 23   |

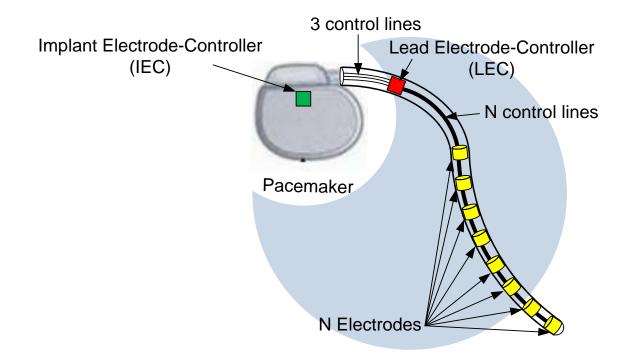

| Figure 0-4: Illustration de système multi-électrodes avec ses deux unités de contrôl          | e à  |

| l'intérieur de l'implant et la sonde (conforme aux normes)                                    |      |

| Figure 0-5: schéma bloc de LEC                                                                | 28   |

| Figure 0-6: les phases différentes du protocole de communication                              |      |

| Figure 0-7: (a) une sonde de stimulation bipolaire simple, (b) une sonde multi-électrodes a   |      |

| LEC, (c) ) une sonde multi-électrodes avec DCU activée qui le transforme en une so            |      |

| bipolaire                                                                                     |      |

| Figure 0-8: schéma bloc de l'unité de contrôde la sonde avec le DCU                           | 33   |

| Figure 0-9: circuit du DCU                                                                    |      |

| Figure 0-10: Microphotographie de la puce DCU                                                 |      |

| Figure 0-11: Remplacement de l'unité de commutation principal et l'unité de connexion         |      |

| défaut par la nouvelle unité de commutation non-volatile à l'intérieur de l'unité de contrôle |      |

| la sonde (LEC)                                                                                |      |

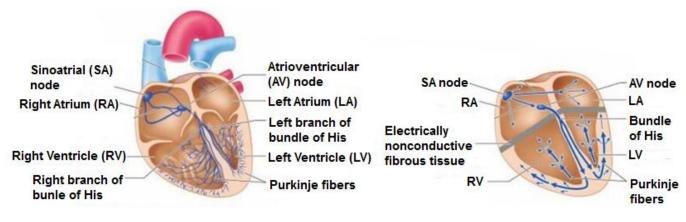

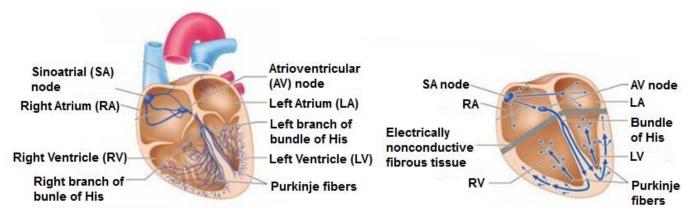

| Figure 2-2: Conduction system of the heart [5]                                                |      |

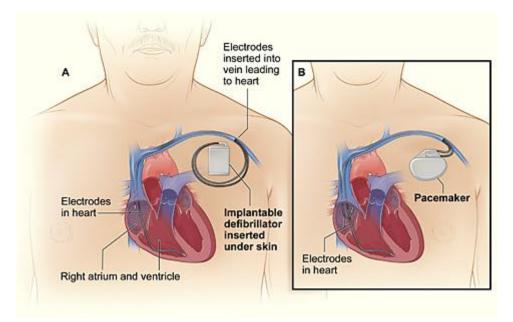

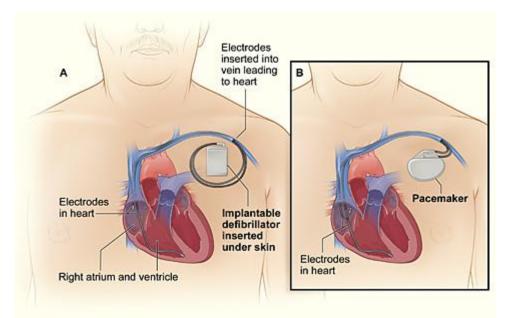

| Figure 2-3: (a) implantable defibrillator (b) Implantable pacemaker [9]                       | 50   |

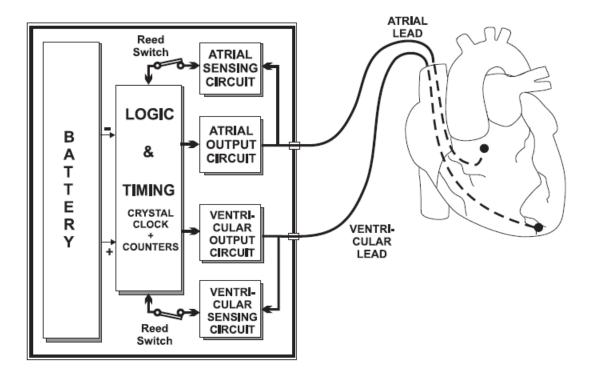

| Figure 2-4: block diagram of Dual chamber pacemaker [8]                                       |      |

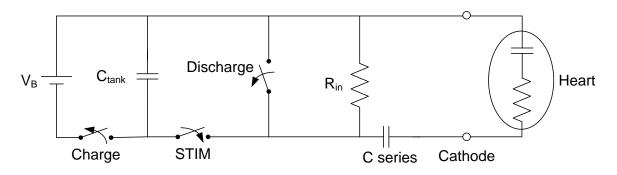

| Figure 2-5: simple circuit diagram for a stimulation channel                                  |      |

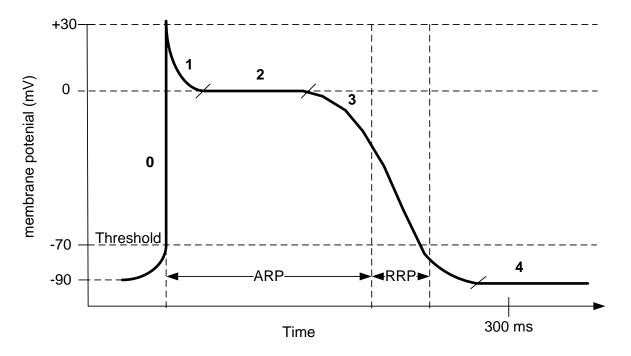

| Figure 2-6: membrane potential during ventricular action potential                            |      |

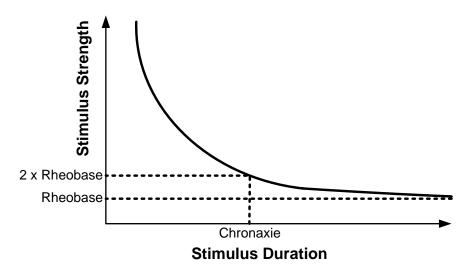

| Figure 2-7: strength-duration curve                                                           |      |

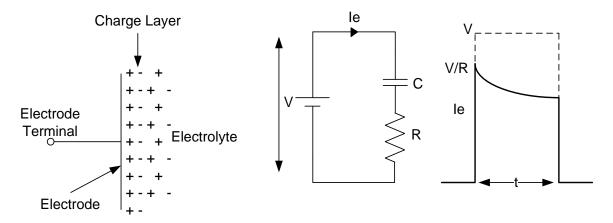

| Figure 2-8: a) electrode-tissue interface b) interface equivalent circuit c) ideal and        |      |

|                                                                                               |      |

| stimulation pulse                                                                             |      |

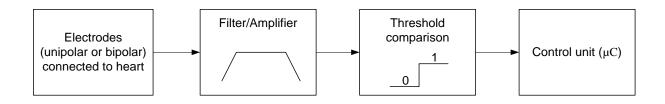

| Figure 2-9: sensing channel block diagram                                                     |      |

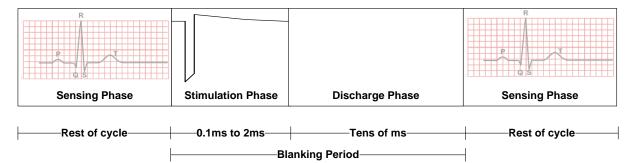

| Figure 2-10: Main phases of pacing cycle in a cardiac pacemaker                               |      |

| Figure 2-11: (a) endocardial leads [22] (b) Epicardial leads [23]                             |      |

| Figure 2-12: Illustration of unipolar stimulation/sensing                                     |      |

| Figure 2-13: Illustration of bipolar stimulation/sensing                                      |      |

| Figure 2-14: CRT pacemaker with three stimulation leads connected                             |      |

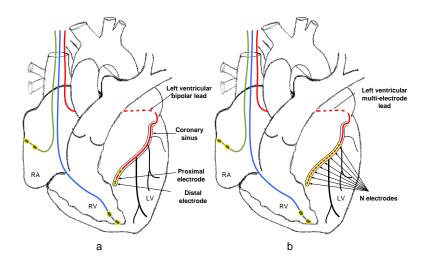

| Figure 3-1 : (a) illustration for the positions of bipolar leads in the different heart chamb |      |

| (b) multi-electrode lead replaces the bipolar left ventricular lead of figure (a)             |      |

| Figure 3-2: Multi-electrode system components. The number of control lines equals             |      |

| number of electrodes in the lead                                                              |      |

| Figure 3-3: Illustration of multi-electrode system with its two control units in the implant  |      |

| inside the lead (norm compliant)                                                              |      |

| Figure 3-4: Centralized structure for the multi-electrode system                              |      |

| Figure 3-5: Distributed structure for the multi-electrode system                              |      |

| Figure 3-6: Abstraction of the main parts of the system implementation                        |      |

| Figure 3-7: (a) phases of conventional pacing cycle (b) pacing cycle after the insertion of   |      |

| multi-electrode preparation phase                                                             |      |

| Figure 3-8: block diagram of the LEC (centralized structure)                                  |      |

| Figure 3-9: example for bidirectional communication between IEC and LEC                       |      |

| Figure 3-10: the different phases of the communication protocol                               | . 82 |

| Figure 3-11: different types of bits that compose the configuration train                     | . 83 |

| Figure 3-12: Example of error in estimation during calibration phase. (LEC; Lead-Electr       | ode  |

| Controller)                                                                                   |      |

| Figure 3-13: Example of error in data decoding due to frequency difference                    | . 85 |

| Figure 3-14:Biphasic stimulation pulses as an example of double stimulation mode              |        |

|-----------------------------------------------------------------------------------------------|--------|

| Figure 3-15: Block diagram of multi-electrode system (distributed structure)                  |        |

| Figure 3-16: LEC chip microphotograph                                                         |        |

| Figure 3-17: Errors in decoding before and after the application of our communic              |        |

| protocol                                                                                      |        |

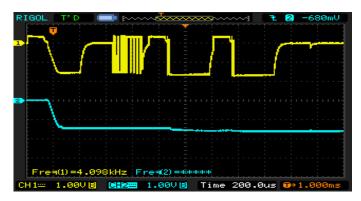

| Figure 3-18: signal on P&C line as observed during chip validation                            | 91     |

| Figure 4-1: (a) Simple bipolar stimulation lead, (b) Multi-electrode stimulation lead w       | ith an |

| electrode-controller LEC, (c) Multi-electrode stimulation lead with the DCU activ             | ivated |

| resulting in a bipolar lead                                                                   | 97     |

| Figure 4-2: Lead Electrode Controller blockdiagram including the DCU                          | 99     |

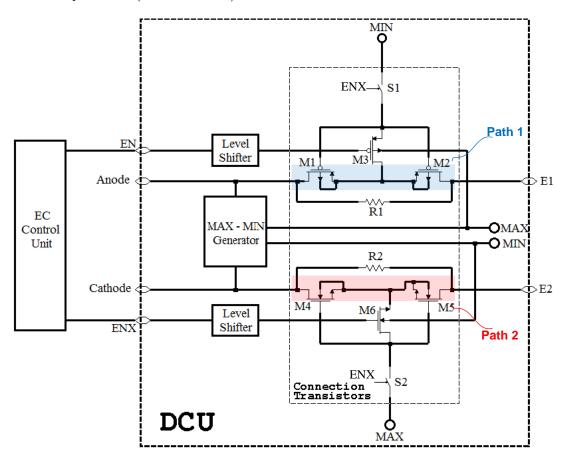

| Figure 4-3: DCU circuit                                                                       |        |

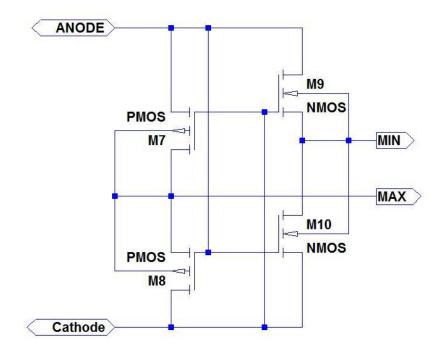

| Figure 4-4: MAX-MIN generator circuit                                                         |        |

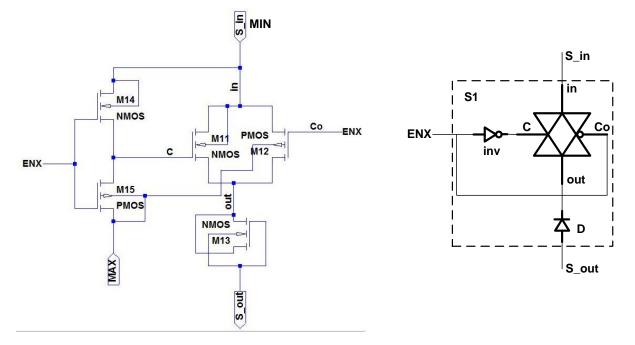

| Figure 4-5: circuit and symbol of S1 switch                                                   |        |

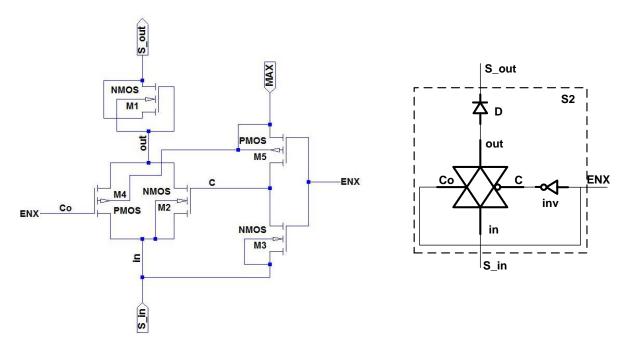

| Figure 4-6: Circuit and symbol of S2 switch                                                   |        |

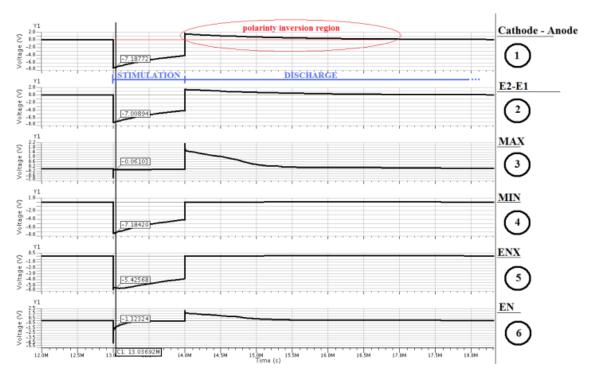

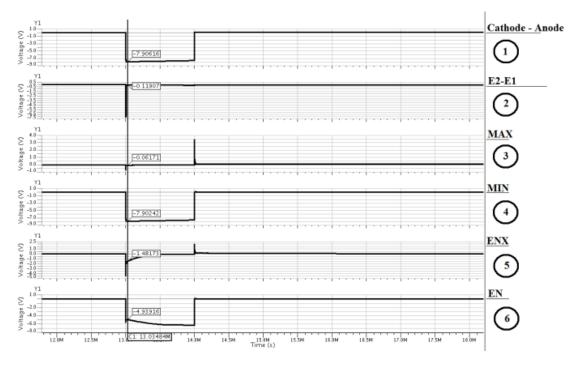

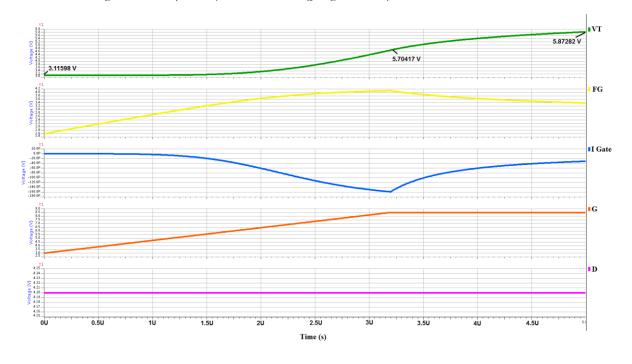

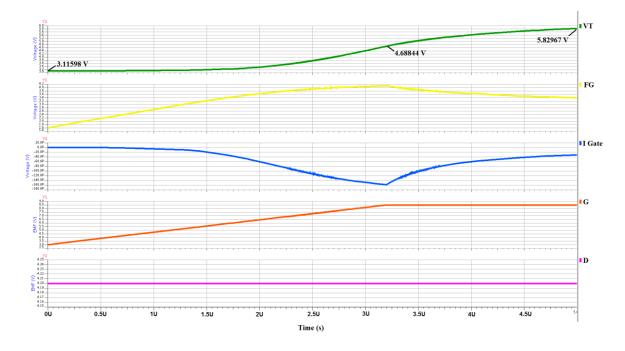

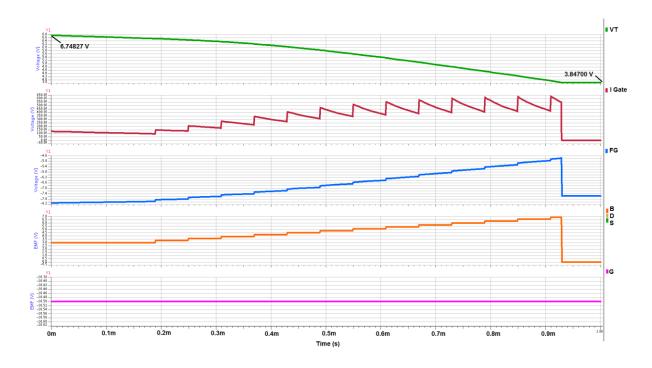

| Figure 4-7: Simulation results of DCU in its active state                                     |        |

| Figure 4-8: Simulation results of DCU in its inactive state                                   |        |

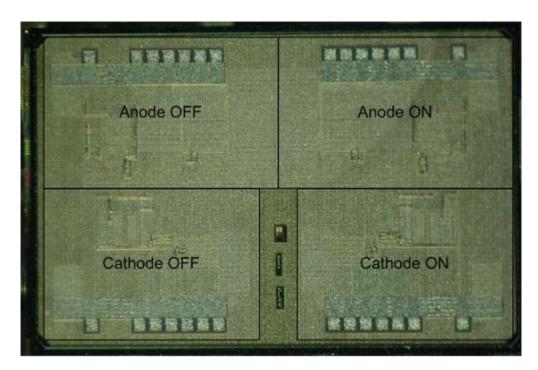

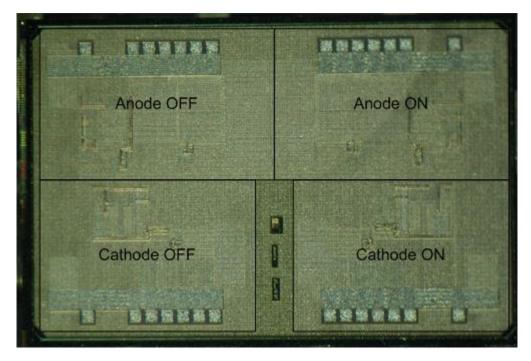

| Figure 4-9: DCU chip microphotograph                                                          |        |

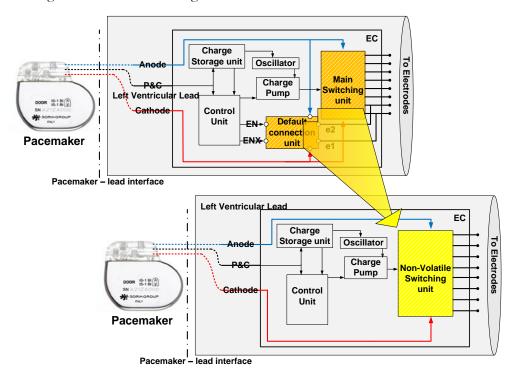

| Figure 5-1: Replacement of main switching unit and default connection unit by the new         |        |

| volatile switching unit inside the lead electrode-controller unit                             |        |

|                                                                                               |        |

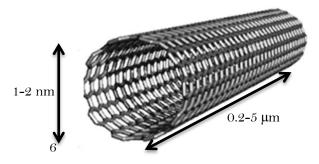

| Figure 5-2: single walled carbon nanotube [18]                                                |        |

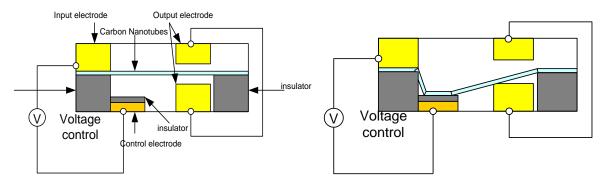

| Figure 5-3: NRAM cell in erased state (left) Programmed state (right) [24]                    |        |

| Figure 5-4: measured values for ON/OFF resistances (left), measured voltages and cu           |        |

| (right) [16]                                                                                  |        |

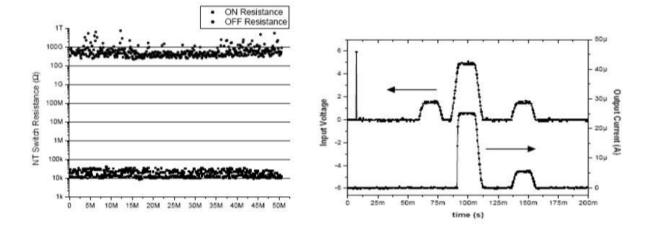

| Figure 5-5: An example for the non-volatile switching unit in the multi-electrode system      |        |

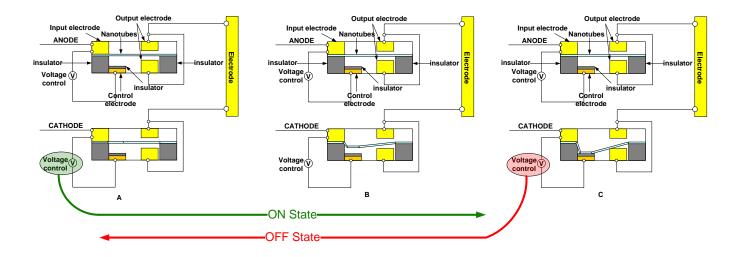

| Figure 5-6: MTJ states [2]                                                                    |        |

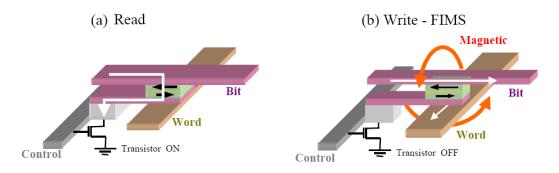

| Figure 5-7: FIMS cell (a) read phase (b) write phase [13]                                     |        |

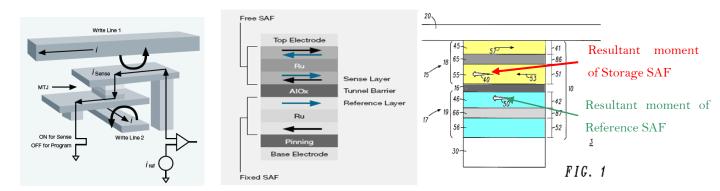

| Figure 5-8: toggle cell anatomy - SAF layers [17, 18]                                         |        |

| Figure 5-9: toggle sequence                                                                   |        |

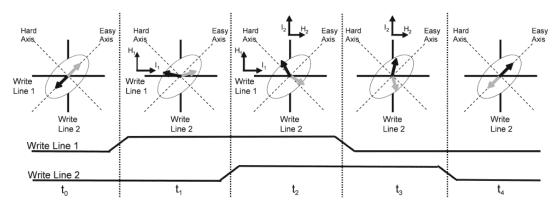

| Figure 5-10: STT structure [2]                                                                | 126    |

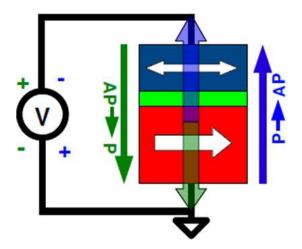

| Figure 5-11: Memristance model                                                                | 128    |

| Figure 5-12: Memristance Voltage and current curves                                           | 129    |

| Figure 5-13: (a) memristance symbol (b) behavioral model circuit in LT Spice                  |        |

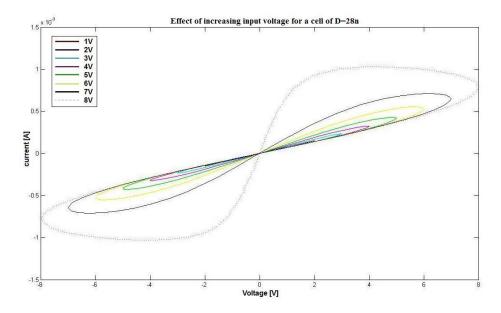

| Figure 5-14: (upper pane) input voltage sine wave of amplitude 1V and 0.5 Hz frequencies      | uency  |

| against the measured current across the cell. (lower pane) the variation of state varia       |        |

| with the input voltage                                                                        |        |

| Figure 5-15: plot of voltage against current presented in the upper pane of fig. 5-14. The    |        |

| is the double hysteresis curve                                                                |        |

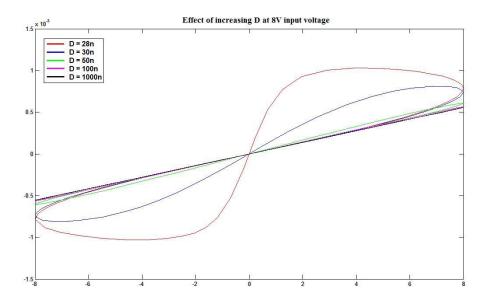

| Figure 5-16: effect of increasing the full length D of the model on the double hysteresis     |        |

| (behavior)                                                                                    |        |

| Figure 5-17: recheck of model correct behavior at all the voltage range after increasing      |        |

| 28nm                                                                                          | -      |

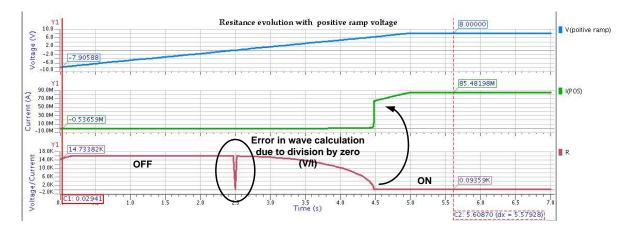

| Figure 5-18: model's resistance evolution with an applied positive ramp voltage signal        |        |

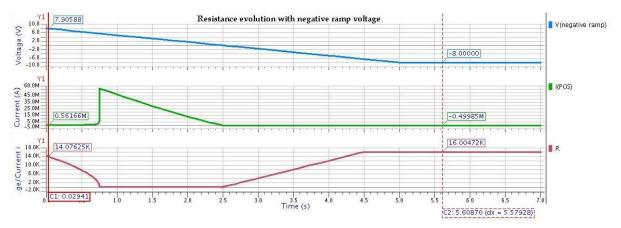

| Figure 5-19: model's resistance evolution with an applied positive ramp voltage signal.       |        |

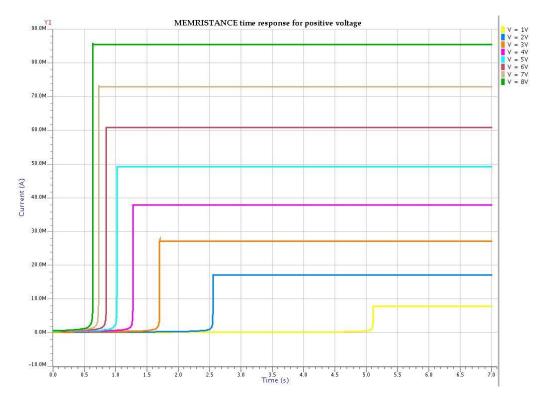

| Figure 5-20: Memristance model switching delay for different positive voltage applied a       |        |

| the cell                                                                                      |        |

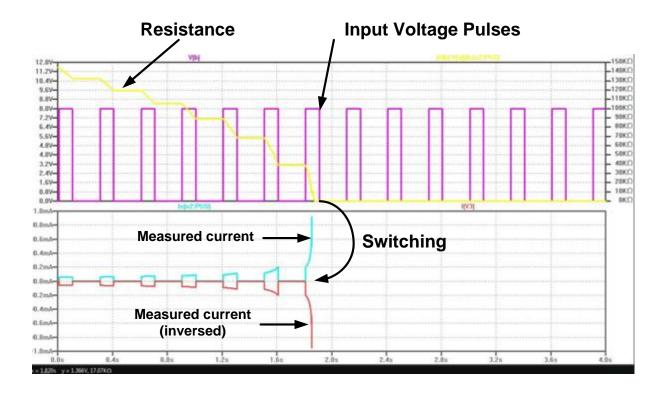

| Figure 5-21: (upper pane) applied positive voltage pulse sequence and the memristance         |        |

|                                                                                               |        |

| resistance is plotted. (lower pane) the measured current across the cell in the two direct    |        |

| The missing part of the current waveform signifies a stable current value                     |        |

| Figure 5-22: Flash memory cell showing the structure of its floating gate transistor $[20]$ . |        |

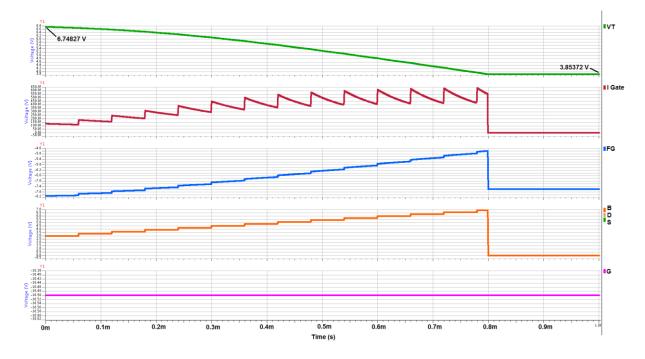

| Figure 5-23: Programming window of flash cell [20]                                            | 137    |

| Figure 5-24: symbol for the generated flash cell - Program sequence                         |

|---------------------------------------------------------------------------------------------|

| Figure 5-25: Program sequence waveforms for reference VerilogA Flash cell140                |

| Figure 5-26: Program sequence waveforms for the generated symbol of Flash cell              |

| Figure 5-27: Symbol for the generated flash cell - Erase sequence                           |

| Figure 5-28: Erase sequence waveforms of reference VerilogA Flash cell                      |

| Figure 5-29: Erase sequence waveforms for the generated symbol of Flash cell 142            |

| Figure 5-30: (a) default operation window of the flash cell model, (b) application adapted  |

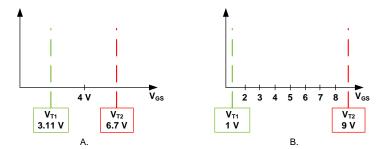

| operation window of the model143                                                            |

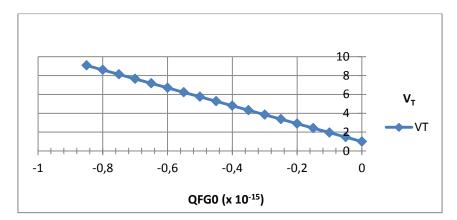

| Figure 5-31: Threshold voltage change with varying QFG0 @Vtuv = 1V144                       |

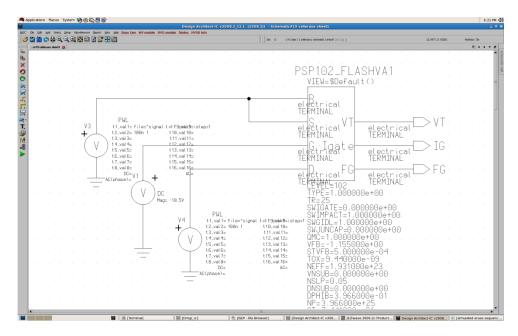

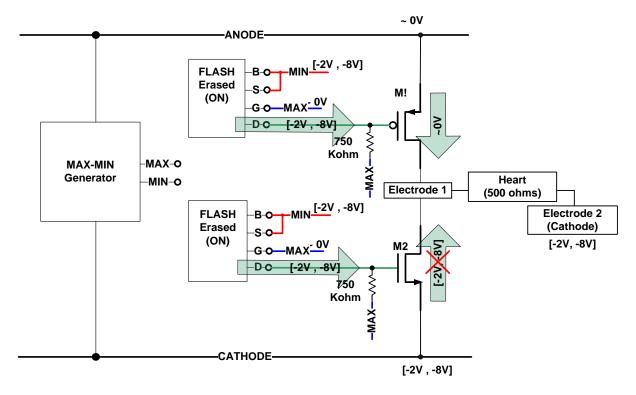

| Figure 5-32: concept schematic                                                              |

| Figure 5-33: Flash cell erased (ON) to block the connection between Cathode and Electrode1  |

|                                                                                             |

| Figure 5-34:Flash cell programmed (off)to eneble the connection between Cathode and         |

| Electrode1147                                                                               |

| Figure 5-35: Flash cell is erased (ON) to enable the connection between Anode and           |

| Electrode1148                                                                               |

| Figure 5-36: Flash cell is programmed to block the connection between Anode and Electrode1  |

|                                                                                             |

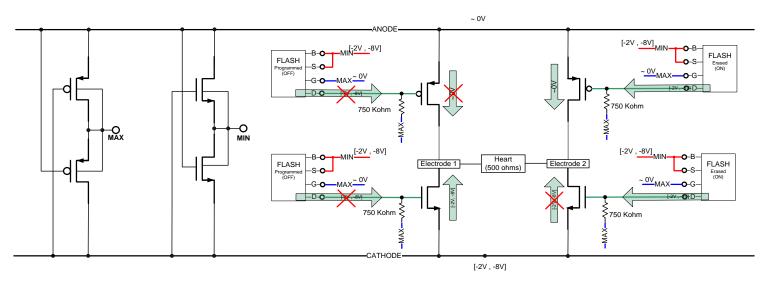

| Figure 5-37: A. Electrode = Cathode, B. Electrode = Anode, C. Electrode = not connected 151 |

| Figure 5-38: example of complete system                                                     |

# List of Tables

| Table 0-1: Charecterictiques de la puce                                             |          |

|-------------------------------------------------------------------------------------|----------|

| Table 2-1: normalized values for stimulation energy [11]                            |          |

| Table 2-2: parameters of stimulation channel                                        |          |

| Table 3-1: Bipolar lead vs. Multi-electrode lead                                    |          |

| Table 3-2: comparison of our solution with other multi-electrode systems found in p | atents88 |

| Table 3-3: Chip Summary                                                             |          |

| Table 4-1: Operation modes                                                          |          |

| Table 4-2: example for MOS sizing                                                   |          |

| Table 4-3: example of capacitance sizing                                            |          |

| Table 4-4: Chip Summary                                                             |          |

| Table 5-1: switching unit specification for cardiac stimulation                     | 117      |

| Table 5-2: NRAM features summary [19, 22]                                           | 119      |

| Table 5-3: STT features                                                             |          |

| Table 5-4: Memristance model parameters [19]                                        |          |

| Table 5-5: typical bias voltages for flash cell [23]                                |          |

| Table 5-6: Characteristics summary                                                  |          |

| Table 5-7: $QFG0 = 0$ and $V_T = 1V$                                                |          |

| Table 5-8: $QFG0 = -8.5e-16$ and $VT = 9.07V$                                       |          |

| Table 5-9: $\overrightarrow{Q}FG0 = 0$ and $VT = 1V$                                |          |

| Table 5-10: $QFG0 = -8.5e-16$ and $VT = 9.07V$                                      |          |

# Résumé de la thèse en Français

## **Chapitre 1: Introduction**

Au cours des dernières années, la qualité des soins s'est beaucoup améliorée. Grace à la recherche dans le domaine de la santé, aux nouvelles découvertes technologiques, les êtres humains vivent non seulement plus longtemps, mais les thérapies suivies sont également de meilleure qualité ; elles réduisent les chances de progression des maladies et permettent leur diagnostique de manière plus précoce. Toutefois, il est important de noter que, malgré ces progrès, il est nécessaire de continuer les efforts de recherche afin de faire face à des pathologies telles que celles liées à des complications cardio-vasculaires qui affectent une grande partie de la population.

Dans plusieurs études, on estime que les maladies cardiovasculaires sont la cause principale de décès, en particulier dans les sociétés industrielles avancées. Aux États-Unis les maladies cardio-vasculaires sont la première cause de décès. Dans le monde entier, on estime à environ 40% le taux de décès résultant de complications cardiaques.

Dans cette thèse, nous nous pencherons sur les implants cardiaques utilisés dans le traitement cardio-vasculaire, en particulier les stimulateurs cardiaques et les défibrillateurs. Nous nous pencherons sur la description de base de ces appareils d'un point de vue électronique et nous allons également présenter leurs évolutions. En outre, nous présenterons nos résultats de recherche qui contribuent tant à l'amélioration de la fonctionnalité qu'à l'augmentation de l'efficacité de ces dispositifs en terme de volume, de performances et de consommation en puissance. Le plan de cette thèse est le suivant:

Au chapitre 2, nous présentons le fonctionnement de base du cœur, les maladies cardio-vasculaires importantes et les dispositifs utilisés pour gérer ces maladies. Nous détaillons l'évolution des implants cardiaques et de leurs composants de base. Par la suite, nous analysons en détail l'insuffisance cardiaque, une des maladies cardio-vasculaires les plus répandues. Par ailleurs, nous discutons de la stimulation bi-ventriculaire qui est le mécanisme utilisé pour gérer l'insuffisance cardiaque.

Au chapitre 3, nous présentons un système multi-électrodes pour résoudre le problème de la stimulation bi-ventriculaire. Nous présentons les défis de conception, la méthodologie de conception et les contraintes d'un tel système. Nous détaillons également les solutions existantes et leurs limites. Enfin, nous présentons les performances et les résultats du système qui a été conçu.

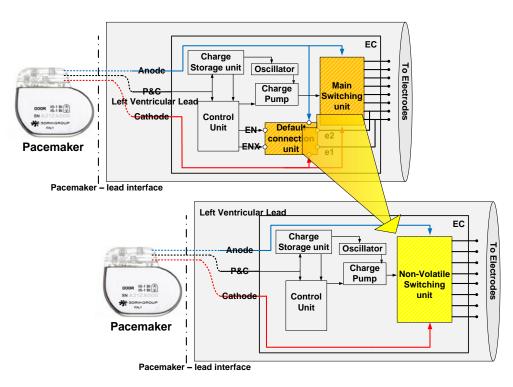

Au chapitre 4, nous détaillons la conception d'un bloc supplémentaire du système multi-électrodes que nous avons présenté dans le chapitre 3. L'ajout de ce bloc à notre sonde multi-électrodes permet de résoudre le problème de la compatibilité de notre système avec les stimulateurs cardiaques existants. Nous présentons en détail la méthodologie de conception, les contraintes et les performances de ce système.

Au chapitre 5, nous examinons les nouvelles technologies au-delà du CMOS standard, visant à rendre notre sonde multi-électrodes plus intelligente, plus petite et plus performante. Nous présentons plusieurs technologies candidates qui peuvent être utilisées dans notre système. Nous discutons de leurs points forts, leurs points faiblesses. Finalement, au travers de simulations nous démontrons la faisabilité de l'utilisation de certaines de ces technologies dans le cadre de l'application visée.

Les principales contributions de cette thèse sont les suivants:

**Conception et mise en œuvre d'un système multi-électrodes:** Nous avons conçu et mis en œuvre un système multi-électrodes qui est capable de stimuler plusieurs sites dans la chambre cardiaque. Notre solution est entièrement configurable et répond aux contraintes de taille et de consommation en puissance imposée par la nature de notre application. Notre puce a été fabriquée en technologie 0,18 µm et occupe 2.25x5.35 mm<sup>2</sup>. La puce, conforme aux normes en vigueur dans le domaine médical, dispose également d'un protocole de communication dédié. Il permet un fonctionnement à faible puissance et permet une configuration rapide. A notre connaissance, notre étude est la première publiée dans son genre.

**Conception et mise en œuvre de l'unité de connexion par défaut:** Nous avons implémenté une unité de connexion par défaut pour la puce multi-électrodes qui a permis l'exploitation de notre sonde multi-électrodes par des stimulateurs cardiaques qui ne sont pas conçus spécifiquement pour le contrôle de cette dernière. La solution élargit donc la compatibilité de notre sonde à tous les stimulateurs cardiaques du marché. Dans ce chapitre, nous discutons et nous apportons des solutions aux principaux défis liés à un environnement très contraignant comme celui du cœur humain. Cette unité a été fabriquée en technologie 0,18  $\mu$ m, elle occupe 2,2 x 1,75 mm<sup>2</sup> de surface. Cette unité est capable de récupérer l'énergie nécessaire de son fonctionnement depuis l'énergie de stimulation envoyée au cœur.

Preuve de faisabilité de l'intégration des technologies de mémoire non volatile dans le système multi-électrodes: De nouvelles technologies ont été explorées qui améliorent

considérablement les performances du système multi-électrodes. L'emploi de ces technologies a amélioré notre système en éliminant le besoin de configuration répétitive des électrodes, économisant ainsi la consommation en puissance et réduisant la latence. Des avantages supplémentaires ont été obtenus au niveau de la taille de la puce et sa compatibilité avec tout autre stimulateur sur le marché. Nous avons exploré plusieurs technologies non volatiles, comme les NRAM, MRAM, Memristance et Flash. Grâce aux simulations, nous avons prouvé la faisabilité de ces technologies pour nos applications. Nous croyons que ces technologies seront utilisées pour concevoir la prochaine génération des sondes à faible puissance et haute performance.

## Chapitre 2: Les Implants de Stimulation Cardiaque

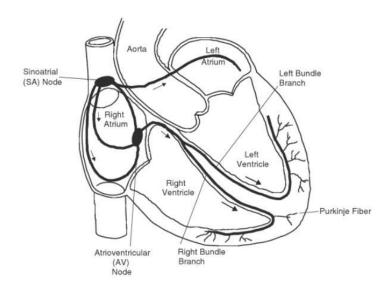

Dans ce chapitre, on parle d'abord du fonctionnement de base du cœur et les disfonctionnements possibles du système cardiovasculaire. Puis on parlera de l'évolution des implants cardiaques utilisés dans le traitement de ces disfonctionnement ou maladies.

Figure 0-1: système de conduction du cœur

### Le cœur humain et l'évolution de l'implant cardiaque

Le cœur est composé de quatre cavités, deux cavités reçoivent le sang désoxygéné de différentes parties du corps, et deux cavités pompent le sang oxygéné de nouveau pour les parties du corps. Si jamais la quantité de sang pompé par le cœur est diminuée pour une raison quelconque, cela pourrait provoquer une perte de connaissance ou même la mort (l'insuffisance cardiaque).

Le fonctionnement du cœur est maintenu par un système de conduction électrique très complexe. Toute activité électrique dans un cœur normal est initiée par le nœud sino-auriculaire connu comme le pacemaker naturel du cœur. L'impulsion électrique se propage dans le système de conduction du cœur comme illustré dans la figure 0-1. Toute perturbation dans ce système de conduction conduit à une condition pathologique critique connue sous le nom d'arythmie.

Les implants cardiaques de nos jours offrent le traitement requis pour beaucoup de maladies comme l'insuffisance cardiaque et la protection contre les situations potentiellement mortelles comme les arythmies.

Le premier pacemaker implantable stimulait le cœur avec des impulsions électriques d'une largeur et d'amplitude fixes à une fréquence fixée à 60 battements par minute. Ensuite, un nouveau concept a été introduit par l'arrivée de ce qu'on appelle « On Demand Pacemaker » où l'activité du cœur est détectée grâce à un simple capteur dans le pacemaker et en fonction de cela, la stimulation adéquate est générée. Cette nouveauté a contourné les inconvénients de la stimulation à fréquence fixe.

Avec la recherche permanente dans l'optimisation de la stimulation cardiaque en fonction des besoins du patient, une étape supplémentaire a été franchie au-delà de la simple détection de l'activité électrique du cœur du patient. Dans les années 1980, des capteurs plus intelligents ont été incorporés dans le stimulateur cardiaque pour mesurer certains paramètres relatifs à l'activité physique du patient tels que le mouvement du corps, la respiration et la pression artérielle

### Système de stimulation cardiaque implantable

Les implants cardiaques sous ses deux déclinaisons – pacemaker ou défibrillateur - se composent d'un générateur d'impulsion électrique implanté sous la peau de la poitrine. Ce générateur est branché au cœur au moyen d'une sonde électriquement isolée de l'extérieur et insérée puis fixée à l'intérieur de cœur (figure 0-2). Les sondes de stimulation sont équipées à leur extrémité par des électrodes pour faire l'interface électrique avec les tissues cardiaques.

Figure 0-2: (a) défibrillateur Implantable (b) Pacemaker Implantable

Le nombre de sondes à insérer dans le cœur varie en fonction du nombre des cavités du cœur à stimuler selon l'état du patient et la décision de son médecin. Soit une cavité (l'oreillette droite RA), soit deux cavités (l'oreillette droite RA et le ventricule droit RV) ou au maximum trois cavités en ajoutant le ventricule gauche LV comme dans le cas de la thérapie de resynchronisation cardiaque (CRT).

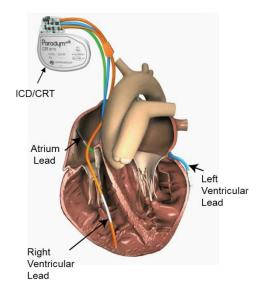

### Thérapie de resynchronisation cardiaque (CRT)

La contraction ventriculaire non synchronisée est l'un des principaux symptômes de l'insuffisance cardiaque. Les dispositifs de CRT traitent ce problème par la stimulation de deux ventricules RV et LV simultanément afin de resynchroniser leurs contractions.

Comme illustré dans la figure 0.3, les sondes de l'oreillette droite RA et le ventricule droit RV sont insérées et fixées à l'intérieur de ces cavités. Contrairement au cas du ventricule gauche, où la sonde doit être fixée à l'extérieur de la cavité. La sonde est insérée à travers une des veines ventriculaires au voisinage de la paroi externe du ventricule gauche (paroi libre). Une fois la paroi libre du ventricule gauche atteinte, une position stable de la sonde doit être obtenue avec la meilleure réponse cardiaque à la stimulation.

Figure 0-3: CRT pacemaker avec trios sondes de stimulation connectés au cœur

En plus de cette procédure compliquée, une stimulation ventriculaire gauche connaît un certain nombre de difficultés telles que:

- La stimulation du nerf phrénique souvent provoquée par la stimulation du ventricule gauche qui génère des effets indésirables chez le patient comme le hoquet et les crampes abdominales. Un moyen d'éviter cela est de placer la sonde dans une autre veine. Si cela n'est pas possible, certaines études ont montré que cela peut être évité en changeant la distance inter-électrode dans la sonde

- Le choix limité du site de stimulation pour le médecin face à la diminution de diamètre de la veine qui l'oblige à fixer le conducteur à un certain point et choisir le meilleur site de

stimulation disponible. L'emploi d'un nombre limité d'électrodes à l'intérieur de la sonde bipolaire limite encore davantage ce choix dans les veines du ventricule gauche

• le déplacement de la sonde qui peut causer une inhibition de la réponse cardiaque à la stimulation. Dans ce cas, une autre intervention chirurgicale semblable à la première est nécessaire afin de repositionner la sonde ventriculaire gauche.

Ce type de complications est inévitable à cause des sondes bipolaires ordinaires qui ne proposent pas une solution non-invasive. Pour cela nous présenterons dans le prochain chapitre le processus de conception d'un système multi-électrodes de stimulation qui pallie les limites de la stimulation ventriculaire gauche.

## Chapitre 3: Système Multi-Electrodes Pour La Stimulation Ventriculaire Gauche: Conception et Mise en Œuvre

Ce chapitre présente un système multi-électrodes pour faire face aux limitations de la stimulation du ventricule gauche. Dans ce chapitre, nous allons montrer comment le système multi-électrodes offre aux médecins une plus grande souplesse dans le choix du meilleur site de stimulation pour leurs patients, ce qui permet une meilleure gestion de la stimulation du nerf phrénique. En outre, nous verrons aussi que le système de multi-électrodes réduit considérablement la probabilité des interventions chirurgicales qui est nécessaire pour repositionner la sonde en cas de déplacement de cette dernière. Ainsi, la sonde multi-électrodes permet un meilleur traitement et une meilleure gestion des maladies cardiaques.

### Système Multi-Electrode : Principe & Contraintes

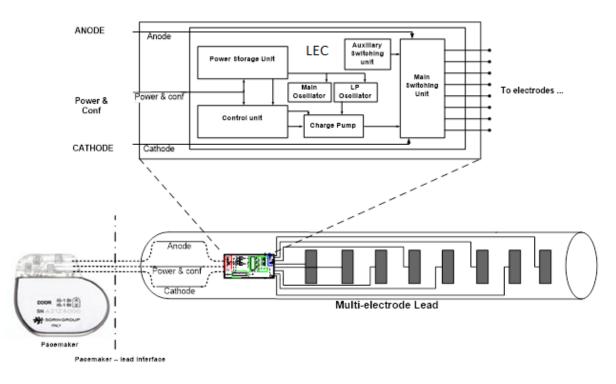

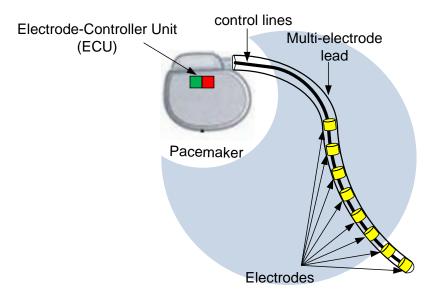

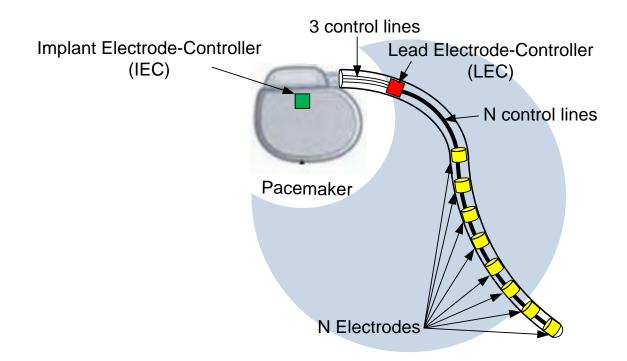

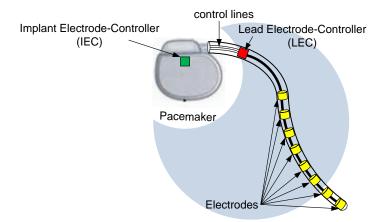

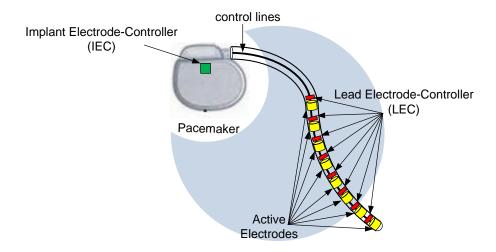

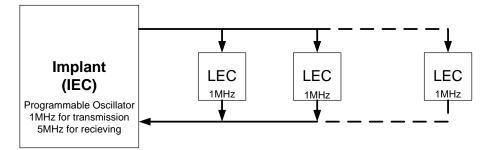

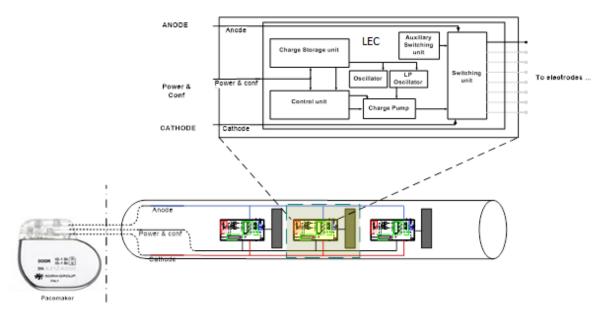

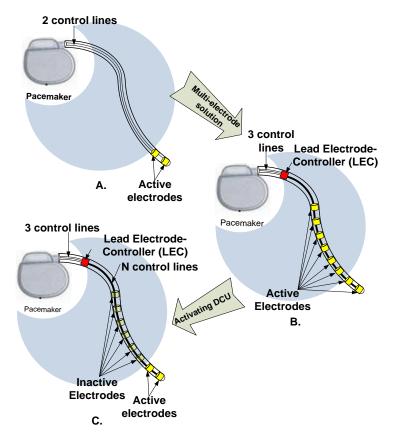

La figure 0-4 montre le système multi-électrodes et ses composants. Similaire aux systèmes classiques de stimulation cardiaque, le système multi-électrodes est composé d'un implant (pacemaker), une sonde multi-électrodes et des électrodes. En raison de la multiplicité des électrodes destinées à être activés sélectivement, un contrôleur d'électrode est nécessaire pour définir l'activité et la polarité de chaque électrode individuellement dans la sonde.

Comme tout système, notre système multi-électrodes avait ses contraintes qui nous ont poussé de trouver des solutions de contournement en phase de conception. La première contrainte était comment contrôler l'ensemble des électrodes (plus que 3 électrodes) dans la sonde tout en respectant les normes qui limitent le nombre de fils qui traversent le connecteur de l'implant à 2 ou 3 fils. Nous avons fait un choix de conception de distribuer le contrôleur des électrodes sur deux parties. La première réside dans l'implant même (Implant Electrode Controller - IEC), et la deuxième est transférée de l'implant à la sonde (Lead Electrode Controller - LEC) comme c'est illustré dans la figure 0-4. De cette façon le nombre de fils qui traversent le connecteur est de 2 ou 3 (conforme à la norme) et chaque électrode a son fil de contrôle. IEC et LEC communiquent mutuellement via 2 à 3 fils de contrôle.

Figure 0-4: Illustration de système multi-électrodes avec ses deux unités de contrôle à l'intérieur de l'implant et la sonde (conforme aux normes)

Ayant choisi d'utiliser un contrôleur d'électrodes séparé à l'intérieur de la sonde, nous avons été confrontés au défi évident de son alimentation. La taille du LEC à l'intérieur de la sonde doit être très petite qui exclut l'utilisation d'une batterie comme source d'alimentation possible. Nous avons donc choisi d'alimenter ce LEC par le stimulateur via un fil dédié.

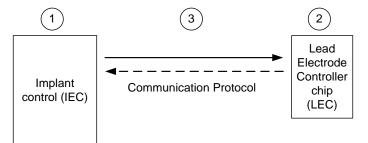

Puisque le IEC dans l'implant doit contrôler le LEC pour configurer/gérer les électrodes, un protocole de communication est nécessaire entre eux. Par ailleurs, afin de minimiser le nombre de fils, nous avons choisi de réutiliser le même fil que nous avions utilisé pour l'alimentation. Le protocole de communication adopté pour notre système sera discuté en détail dans ce chapitre.

### Conception et implémentation du système

Nous avons fait le choix d'utiliser une interface à 3 fils entre le connecteur et le stimulateur LEC. 2 fils (anode et cathode) sont utilisés exclusivement pour la stimulation et l'acquisition de signaux cardiaques. La troisième ligne est dédiée au protocole de communication entre le stimulateur cardiaque (maître) et le LEC (esclave). Ce protocole de communication porte l'alimentation et les bits de configuration nécessaires pour la fonctionnalité du LEC. L'avantage de cette méthode est que ni les impulsions d'alimentation ni les données ne sont mélangées avec les lignes de stimulation.

Par ailleurs, nous nous sommes engagés à assurer la compatibilité de notre sonde multi-électrodes avec tous les stimulateurs du marché. Nous l'avons pris en compte en mettant en place une unité de commutation auxiliaire dans le LEC dont le rôle est de garder un lien actif entre le stimulateur cardiaque et le cœur du patient par au moins deux électrodes sans aucune consommation d'énergie. Cette unité auxiliaire permet également d'obtenir une faible consommation d'énergie pour l'ensemble du système.

Nous avons également inclue une fonction supplémentaire appelée stimulation double. Elle permet d'appliquer deux impulsions de stimulation consécutives. La première et la deuxième stimulation peuvent être soient appliquées sur la même configuration d'électrodes ou sur deux configurations différentes. Cette fonction ouvre une voie de recherche clinique qui peut démontrer son utilité dans l'amélioration de la stimulation cardiaque.

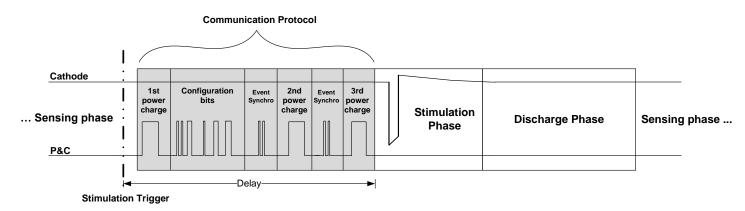

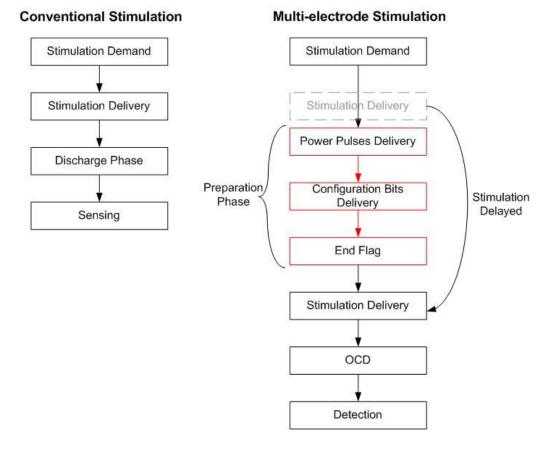

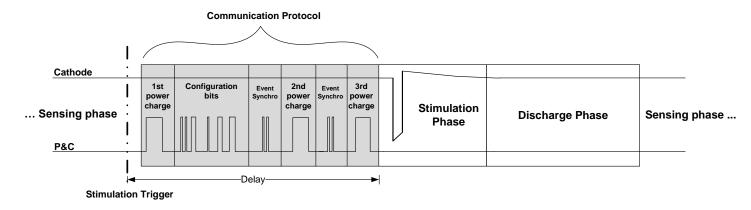

Une unité de contrôle à l'intérieur d'un implant classique (pacemaker) gère la séquence d'actions et d'événements au sein du cycle de stimulation. Ce cycle de stimulation se compose de trois phases: la détection, la stimulation et la décharge

- Lors de la phase de détection, la chaine de détection d'un pacemaker filtre et analyse les signaux cardiaques acquis pour détecter des troubles de l'activité cardiaque du patient.

- En cas de trouble cardiaque détecté, une demande de stimulation est générée qui déclenche le circuit de sortie pour démarrer la phase de stimulation et de fournir une impulsion électrique au cœur sur les électrodes configurées.

- Ensuite la phase de décharge élimine les charges résiduelles provenant de l'interface électrode-tissu et le chemin de la stimulation/détection.

Dans notre système multi-électrodes, une phase supplémentaire a été insérée entre la demande de stimulation et sa livraison. Cette phase de préparation a pour mission de fournir à la LEC dans la sonde l'alimentation nécessaire et les bits de configuration des électrodes.

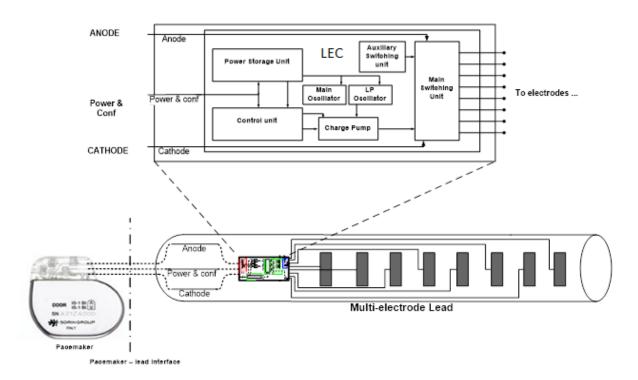

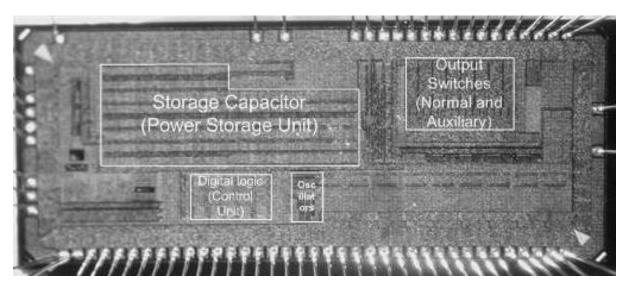

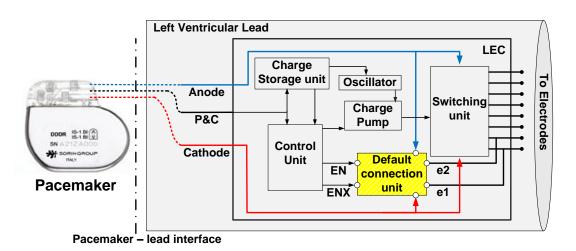

Nous avons conçu la LEC, sous la forme d'un ASIC (Application-Specific Integrated Circuit) pour être inséré à l'intérieur de la sonde, comme illustré dans la figure 0-5 où nous présentons les blocs principaux de la puce LEC.

Figure 0-5: schéma bloc de LEC

L'unité de stockage d'énergie est la seule source d'énergie pour le LEC qui assure sa fonctionnalité pendant un cycle cardiaque complet. Les impulsions d'alimentation envoyées par l'implant sont stockées dans un condensateur dans le LEC. Un condensateur avec une taille considérable serait nécessaire pour maintenir l'énergie suffisante pour le circuit de la puce. Grace au protocole mis en place, plusieurs impulsions de puissance sont prévues pour permettre la réduction de la taille de la capacité de stockage et de la recharger régulièrement.

L'unité de contrôle est la logique dans laquelle le protocole de communication est mis en œuvre. Le rôle premier de cette unité est de faire la différence entre les impulsions électriques et les bits de configuration. Elle achemine les impulsions électriques à l'unité de stockage d'énergie, et s'appuie sur des oscillateurs locaux pour décoder les bits de configuration. En outre, l'unité de contrôle active les deux unités de commutation ; principale et auxiliaire à des moments précis selon les données de configuration décodées qui indiquent l'état souhaité et la polarité de chaque électrode dans la sonde

L'unité de commutation principale définit le chemin de la stimulation du stimulateur cardiaque au cœur, elle est composée principalement des commutateurs MOS haute tension afin de supporter des tensions élevées (dizaines de volts) et des courants élevées (des dizaines de mA) de stimulation fournies au cœur.

Le chemin entre le stimulateur et les électrodes configurées doit être maintenu en gardant les commutateurs MOS configurés actif. L'unité de contrôle maintient cette stimulation pendant les phases de décharge. Pendant la phase de détection, l'unité de commutation auxiliaire prend en charge ce rôle pour transmettre les signaux cardiaques au stimulateur.

L'unité de commutation auxiliaire est activée dans le LEC lorsque le niveau d'alimentation diminue. Cette unité est capable de maintenir la connexion entre les électrodes et le stimulateur cardiaque, sans aucune alimentation électrique. Dans une première mise en œuvre, nous avons utilisé des interrupteurs JFET. Ils sont normalement actifs, tandis que pour les déconnecter une alimentation est nécessaire pour forcer l'état inactif. C'est le cas pendant la phase de détection. Il est difficile d'estimer une durée fixe pour cette phase, afin de dimensionner le condensateur de stockage.

Un autre avantage de l'utilisation d'une telle unité de commutation auxiliaire est d'assurer une compatibilité avec n'importe quel stimulateur du marché. Le fait que cette unité est connectée sans source d'énergie, elle assure une connexion minimale dans la sonde multi-électrodes afin d'agir comme une sonde bipolaire simple. Cette connexion est indépendante de tout protocole de communication spécifique qui peut exister dans n'importe quel système multi-électrodes. C'est un atout supplémentaire pour notre système par rapport aux autres solutions multi-électrodes.

#### Protocole de Communication

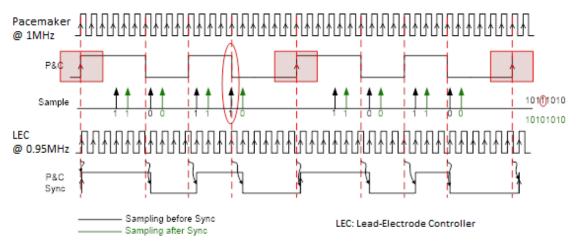

Dans notre mise en œuvre de ce test-chip, nous avons implémenté un protocole de communication unidirectionnel (IEC-> LEC) et nous avons choisi la fréquence d'horloge de l'implant à 1MHz. Cela a ajouté un autre défi pour l'LEC de décoder correctement la configuration envoyée en un seul coup, car il ne sera pas renvoyé d'IEC.

Figure 0-6: les phases différentes du protocole de communication

• Impulsions d'Alimentation:

Les phases de recharge ont été placées avant chaque activité consommant de l'énergie prévue pour les circuits de LEC. En plus du réveil (Wake-Up) du LEC, cette première phase assure qu'il y a suffisamment d'énergie pour la phase de configuration. La dernière phase d'alimentation est placée juste avant la phase de stimulation pour faire en sorte que l'unité de commutation a une énergie suffisante pour maintenir l'état des électrodes configurées lors de la phase de stimulation et la phase de décharge qui intervient juste après.

• Bits de synchronisation d'événements

Ils sont insérés avant les actions à effectuées par le LEC à un moment précis. En outre, ces bits de synchronisation d'événement aident l'unité de contrôle du LEC à différencier entre les bits de communication et les impulsions d'alimentation

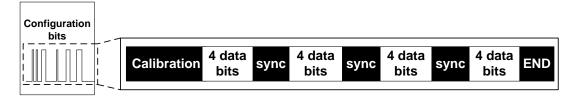

• Bits de configuration

Ils transportent les informations de l'activité et de la polarité de chaque électrode dans la sonde multi-électrodes. Cette information est nommée ici "bits de données". D'autres types de bits tels que "calibration" et "sync" complètent la structure des bits de configuration.

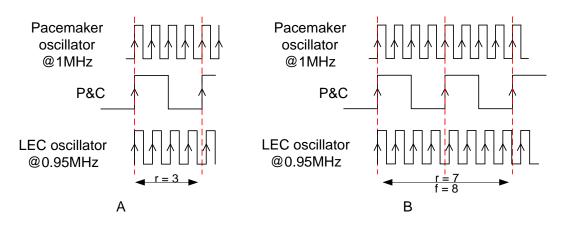

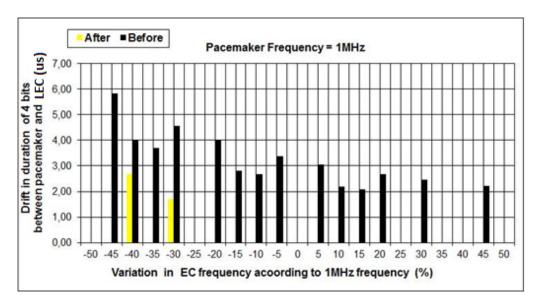

Le décodage de données est basé sur le comptage des cycles d'horloge par bit pour l'acquisition de sa valeur à son milieu. En raison du déphasage entre l'oscillateur du LEC et celui du stimulateur cardiaque qui pourrait à tort estimer le nombre de bits côté LEC, nous mettons en place trois mécanismes:

- Calibration: ce mécanisme évalue le nombre de cycles d'horloge qui composent un bit en fonction de l'oscillateur du LEC.

- Synchronisation des données: dans une trame, un bit de synchronisation est ajouté après chaque 4 bits de données. Cela nous aide à éviter la propagation des erreurs dans la trame. Cette approche est similaire à la communication de données asynchrones « start-stop » utilisées dans la synchronisation de caractère en ASCII.

- Synchronisation de trame : chaque trame est décalée dans le temps de façon à être synchronisé avec l'horloge LEC. Cela garantit que le décodeur compte correctement la longueur de chaque bit uniquement sur la base de cycles d'horloge complets. (En nombre de cycles d'horloge).

### Résultat de Mesure

La puce LEC a été fabriquée en technologie 0.18µm. Cette technologie est adaptée pour la haute tension présente dans l'impulsion de stimulation. Le Tableau 0-1 résume les caractéristiques de la puce.

| Table 0-1: Charecterictiques de la puce       |                                       |

|-----------------------------------------------|---------------------------------------|

| Technologie                                   | 0.18 µm                               |

| Surface                                       | $2.25 \mathrm{x} 5.35 \mathrm{~mm^2}$ |

| Courant moyenne consommee par cycle cardiaque | 206.3 nA                              |

| Temps pour la configuration                   | 2 ms                                  |

| Frequence d'horloge                           | 1 MHz                                 |

| La tension d'operation                        | 1.8V                                  |

| La tolerance sur la frequence d'horloge       | -20% to 40%                           |

Notre protocole de communication mis en œuvre tolère une différence de fréquence de l'oscillateur, que ce soit dans le sens croissant ou décroissant, grâce à la phase d'étalonnage et les calculs ci-joints qui ont permis d'affiner l'estimation de la longueur de bit. L'échelle de fréquence tolérée a été observée entre de -20% à +40% tel que ça apparaît dans le tableau.

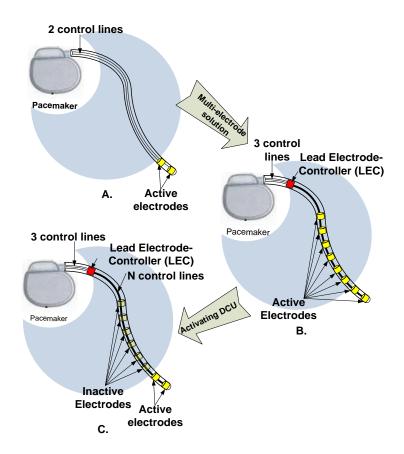

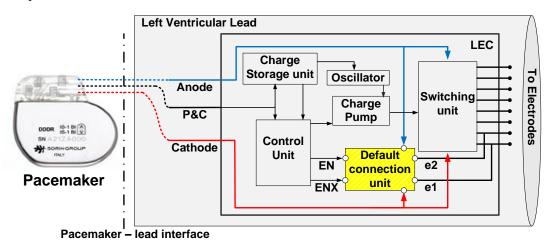

## Chapitre 4: Unité de Connexion Par Défaut

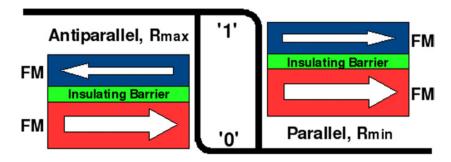

Le système multi-électrodes nécessite la présence de contrôleurs compatibles entre eux dans la sonde et le stimulateur cardiaque (le LEC et IEC). Dans le chapitre précédent, nous avons décrit notre propre implémentation de ces deux contrôleurs, mais dans le monde réel, des situations peuvent surgir qui limitent le fonctionnement d'une telle solution. Une situation, qui se produit fréquemment, est le remplacement du stimulateur cardiaque en raison de l'épuisement de la batterie, ou un dysfonctionnement général du stimulateur cardiaque. Les médecins souvent remplacent les stimulateurs cardiaques implantés par modèle récent.

Toutefois, étant donné que la mise en œuvre de système multi-électrodes est propre à nous, la sonde multi-électrodes ne peut pas être utilisée avec un nouveau stimulateur cardiaque qui n'est pas explicitement conçu pour contrôler le LEC dans la sonde. C'est pourquoi la compatibilité de la sonde est cruciale.

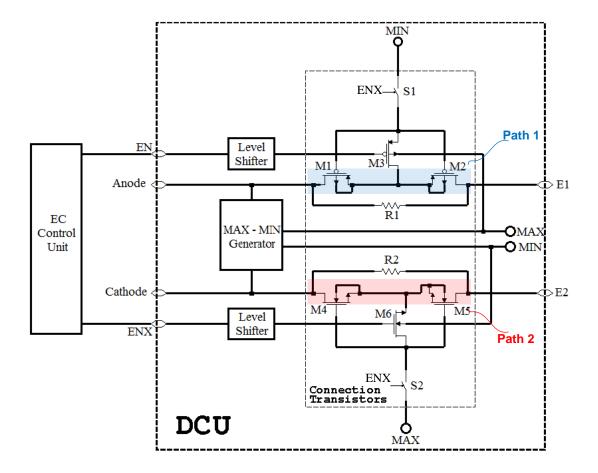

Figure 0-7: (a) une sonde de stimulation bipolaire simple, (b) une sonde multi-électrodes avec LEC, (c) ) une sonde multi-électrodes avec DCU activée qui le transforme en une sonde bipolaire