# Work-conserving dynamic TDM-based memory arbitration for multi-criticality real-time systems

Thèse de doctorat de l'Université Paris-Saclay préparée au CEA, List

Ecole doctorale n°580 Sciences et Technologies de l'Information et de la Communication (STIC) Spécialité de doctorat: Programmation : modèles, algorithmes, langages, architecture

Thèse présentée et soutenue à Palaiseau, le 28/11/2019, par

### FAROUK HEBBACHE

| Composition du Jury :                                 |                    |  |  |  |  |

|-------------------------------------------------------|--------------------|--|--|--|--|

| Alain Mérigot                                         |                    |  |  |  |  |

| Professeur, Université Paris-Sud (UFR Sciences)       | Président          |  |  |  |  |

| Claire Pagetti                                        |                    |  |  |  |  |

| Ingénieur de recherche, ONERA (DTIM)                  | Rapporteur         |  |  |  |  |

| Christine Rochange                                    |                    |  |  |  |  |

| Professeur, Université de Toulouse (IRIT)             | Rapporteur         |  |  |  |  |

| Steven Derrien                                        |                    |  |  |  |  |

| Professeur, Université de Rennes 1 (IRISA)            | Examinateur        |  |  |  |  |

| Frédéric Pétrot                                       |                    |  |  |  |  |

| Professeur, Institut polytechnique de Grenoble (TIMA) | Examinateur        |  |  |  |  |

| Laurent Pautet                                        |                    |  |  |  |  |

| Professeur, Télécom Paris (LTCI)                      | Directeur de thèse |  |  |  |  |

| Florian Brandner                                      |                    |  |  |  |  |

| Maître de conférence, Télécom Paris (LTCI)            | Encadrant          |  |  |  |  |

| Mathieu Jan                                           |                    |  |  |  |  |

| Ingénieur-chercheur, CEA, List (L3S)                  | Encadrant          |  |  |  |  |

|                                                       |                    |  |  |  |  |

## Acknowledgements

Je tiens tout d'abord à remercier grandement mon directeur de thèse, Laurent Pautet et mes deux encadrants Florian Brandner et Mathieu Jan, pour toute l'aide qu'ils m'ont apporté tout au long de cette thèse. Qu'ils soient aussi remerciés pour leurs disponibilités permanentes et pour les nombreux encouragements qu'ils m'ont prodigué.

Le travail qui est présenté dans ce mémoire a été effectué au CEA List au sein du Laboratoire L3S. Aussi, merci à messieurs E. Hamelin, O. Heron et C. Gamrat, de m'avoir accueilli et mis à ma disposition tous les moyens nécessaires aussi bien techniques que financiers, afin de mener à bien ce travail.

Merci à monsieur A. Mérigot pour avoir accepté de présider mon jury de thèse.

Merci à Madame C. Pagetti et madame C. Rochange, pour avoir accepté d'étudier mes travaux et d'en être les rapporteurs.

Merci à messieurs S. Derrien et F. Pétrot de l'attention qu'ils portent à mon travail en acceptant d'être membres du jury.

J'aimerais ensuite remercier toutes les personnes que j'ai rencontrées au L3S tout au long de ma thèse. En particulier, je tiens à remercier mes anciens collègues Daniel V., Martin Z., Philippe G., Emine L., Massinissa A., Belgacem B., Mihail A., et Briag L. pour toutes les discussions intéressantes qu'ont n'a pu avoir. Je voudrais également exprimer ma gratitude à Marie-Isablle G., secrétaire du Département DACLE, pour son aide durons ces trois dernieres années.

Un grand merci à mon épouse Katia pour son soutien inconditionnel et surtout supporté dans tout ce que j'ai entrepris.

Enfin, je voudrais exprimer ma profonde gratitude à mes parents, Ammar et Saliha, ainsi que mes frères et soeur Manaouir, Koceila, Islam et Thiziri pour leurs soutiens et leurs aides.

#### UNIVERSITÉ PARIS SACLAY

# Résumé

#### Arbitrage mémoire dynamique non-oisif basé sur TDM pour des systèmes multi-criticité temps réel

par Farouk HEBBACHE

Les systèmes temps-réel doivent réagir de manière fiable, ce qui implique à la fois d'être certain du résultat produit par leurs programmes mais aussi de connaître le temps qu'ils prennent pour s'exécuter. Les pire temps d'exécution sont ainsi des données fondamentales pour la validation et la sûreté de tels systèmes temps-réel, et encore plus dans le contexte des systèmes temps-réel autonomes (robotique, voiture autonome) pour lesquels la sûreté de fonctionnement est primordiale.

Cependant calculer un pire temps d'exécution (dit WCET pour Worst-Case Execution Time), à la fois garanti (majorant strict) et pas trop pessimiste afin de réduire les coûts et la complexité de tels systèmes temps-réel, est un problème difficile à résoudre sur des architecture matérielles multi-cœurs. Une difficulté est la concurrence d'exécution entre différents programmes souhaitant accéder à une ressource partagée, typiquement une mémoire. Pour chaque requête d'accès à une telle ressource partagée émise par un programme, il faut en effet systématiquement considérer la situation la plus défavorable induite par la politique d'arbitrage utilisée. Ceci induit un pessimisme important dans la valeur du WCET obtenue et donc un faible taux d'utilisation de cette ressource partagée lors de l'exécution des programmes. Ce problème de sous-utilisation de la ressource partagée est amplifié par la multiplication de programmes non-soumis à des contraintes temporelles (dits programmes non-critiques) qui s'exécutent en parallèle des programmes temps-réel (dits programmes critiques). Les requêtes d'accès générées par ces programmes non-critiques impactent la situation la plus défavorable qui doit être considéré pour les requêtes d'accès émises par les programmes critiques et accentuent donc le pessimisme des WCET calculés.

Il est possible d'éliminer par construction toute concurrence entre les requêtes d'accès émises par les différents programmes en ayant recours à une politique d'arbitrage à multiplexage temporel (en anglais *Time-Division Multiplexing*, TDM). Selon cette politique, le temps est divisé en créneaux temporels chacun alloué à un programme prédéfini pour un accès exclusif à la ressource partagée. Le temps d'accès à la ressource partagée par un programme peut alors être facilement borné. La bande passante offerte à un programme est indépendante des autres programmes et les WCET des programmes peuvent ainsi être déterminés.

Toutefois, le temps d'accès à la ressource partagée dépend de l'ordonnancement des créneaux temporels qui lui sont affectés. Or cet ordonnancement est généralement statique car réalisé lors de la conception du système, avant l'exécution des programmes. Il comprend généralement l'affectation d'une séquence de créneaux temporels à différents programmes, cette séquence se répétant périodiquement (on parle de période TDM). Mais les créneaux temporels d'une période TDM ne sont utilisés par les programmes que s'ils ont une requête d'accès à la ressource partagée à émettre. Lorsque cela n'est pas le cas, ces créneaux temporels sont donc inutilisés. Une politique d'arbitrage TDM basique est donc dite oisive car ces créneaux temporels ne sont pas récupérés par les autres programmes afin de diminuer leur temps d'accès à la ressource partagée.

Par ailleurs, il est admis que pour les programmes temps-réel, il peut exister une large différence entre le temps d'exécution d'une instance du programme et son WCET. L'oisiveté de la politique d'arbitrage TDM associée à cette caractéristique des programmes temps réel génère un faible taux d'utilisation de la ressource partagée. Ce problème est amplifié lorsque le nombre de programmes augmente car dans ce cas la longueur d'une période TDM est également augmentée. Un autre facteur d'amplification de ce phénomène est la présence au sein des systèmes considérés d'un nombre croissant de programmes non-critiques pour lesquels l'affectation de créneaux augmente la latence des requêtes des programmes critiques ainsi que la latence des requêtes de ces programmes non-critiques, en contradiction avec leur objectif d'avoir les meilleurs performances d'exécution en moyenne.

Les travaux menés dans le cadre de cette thèse présentent une reconstruction de la politique d'arbitrage TDM qui permet d'en réduire l'oisivité. Plutôt que de requérir à un arbitrage au niveau des créneaux TDM, notre approche dynamique fonctionne à la granularité des cycles d'horloge en exploitant du temps gagné par les requêtes précédentes. Cela permet au mécanisme d'arbitrage de réorganiser le traitement des requêtes mémoire, exploiter les latences d'accès réelles des requêtes, et ainsi d'améliorer l'utilisation de la mémoire. Nous démontrons que nos politiques d'arbitrage sont analysables car elles préservent les garanties temporelles qu'offre TDM dans le pire cas, alors que nos expérimentations montrent une meilleure utilisation de la mémoire en moyenne. De plus, une variante de notre stratégie d'arbitrage est présentée et

évaluée dans le cadre d'une implémentation matérielle à faible complexité. Les évaluations montrent que l'implémentation est efficace, tant en matière de complexité matérielle que de performance d'arbitrage concernant l'utilisation de la mémoire.

Pour finir, nous explorons l'applicabilité de nos approches dans le contexte d'un système préemptif, où nos approches peuvent induire du fait d'une préemption des délais de blocage mémoire supplémentaire en fonction de l'historique d'exécution. Ces délais de blocage peuvent induire une gigue importante et par conséquent augmenter les temps de réponse des tâches. Ainsi nous étudions des moyens de gérer et, enfin, de limiter ces délais de blocage. Trois différentes stratégies sont explorées et comparées du point de vue de leur analysabilité, de l'impact sur l'analyse des temps de réponse, et de la complexité de l'implémentation matérielle ainsi que du point de vue du comportement à l'exécution. Les expérimentations montrent que les différentes approches se comportent sensiblement de manière identique au cours de l'exécution. Cela nous permet de retenir l'approche combinant analysabilité et une faible complexité d'implémentation matérielle.

**Mots-clés :** *Time-Division Multiplexing, Arbitrage Dynamique, Calcul Prédictible, Systèmes Multi-*Critiques, Systèmes Temps Réel, Mémoire, Préemption

#### UNIVERSITÉ PARIS SACLAY

# Abstract

# Work-conserving dynamic TDM-based memory arbitration for multi-criticality real-time systems

by Farouk HEBBACHE

Real-time systems have to reliably react, which implies both being confident regarding the result produced by the programs and also knowing how long they take to execute. The Worst-Case Execution Times (WCETs) are thus fundamental information for the validation and reliability of such real-time systems, especially in the context of autonomous real-time systems (robotics, autonomous car, GPS) for which reliability is essential. However, computing a WCET, both guaranteed (strict upper-bound) and also not too pessimistic in order to reduce the costs and complexity of such real-time systems, is a challenging problem to solve on multi-core hardware architectures.

Multi-core architectures pose many challenges in real-time systems, which arise from contention between concurrent accesses to shared memory. Various memory arbitration schemes have been devised that address these issues, by providing trade-offs between predictability, average-case performance, and analyzability. Among the available memory arbitration policies, Time-Division Multiplexing (TDM) ensures a predictable behavior by bounding access latencies and guaranteeing bandwidth to tasks independently from the other tasks. To do so, TDM guarantees exclusive access to the shared memory in a fixed time window. TDM, however, provides a low resource utilization as it is *non-work-conserving*. Besides, it is very inefficient for resources having highly variable latencies, such as sharing the access to a DRAM memory. The constant length of a TDM slot is, hence, highly pessimistic and causes an underutilization of the memory.

To address the aforementioned limitations of TDM, we present, in this thesis, dynamic arbitration schemes that are based on TDM. However, instead of arbitrating at the level of TDM slots, our approach operates at the granularity of clock cycles by exploiting *slack* time accumulated from preceding requests. This allows the arbiter to reorder memory requests, exploit the actual access latencies of requests, and thus improve memory utilization. We demonstrate that our policies are analyzable as they preserve the guarantees of TDM in the worst case, while our experiments show an improved memory utilization. We furthermore present and evaluate an efficient hardware implementation for a variant of our arbitration strategy. Our evaluations showed that the implementation is efficient, both in terms of hardware complexity and arbitration performance regarding the memory utilization.

Finaly, we explore the applicability of our approaches in a preemptive system model, where preemption-related memory blocking times can occur, depending on execution history. These blocking delays may induce significant jitter and consequently increase the tasks' response times. We thus explore means to manage and, finally, bound these blocking delays. Three different schemes are explored and compared with regard to their analyzability, impact on response-time analysis, implementation complexity, and runtime behavior. Experiments show that the various approaches behave virtually identically at runtime. This allows to retain the approach combining low implementation complexity with analyzability.

**Keywords:** Time-Division Multiplexing, Dynamic Arbitration, Predictable Computing, Multi-Criticality Systems, Real-Time Systems, Memory, Preemption

This work is licensed under a Creative Commons "Attribution-NonCommercial-ShareAlike 3.0 Unported" license.

# Contents

| A  | cknov                   | ledgements                               | iii  |  |  |  |  |

|----|-------------------------|------------------------------------------|------|--|--|--|--|

| Re | Résumé v<br>Abstract ix |                                          |      |  |  |  |  |

| A  |                         |                                          |      |  |  |  |  |

| Li | st of                   | ublications                              | xvii |  |  |  |  |

| 1  | Intr                    | duction                                  | 1    |  |  |  |  |

|    | 1.1                     | Context                                  | 1    |  |  |  |  |

|    | 1.2                     | Contribution Overview                    | 2    |  |  |  |  |

|    | 1.3                     | Thesis Outline                           | 4    |  |  |  |  |

| Ι  | Ba                      | kground/State of the art                 | 7    |  |  |  |  |

| 2  | Rea                     | Time Systems                             | 9    |  |  |  |  |

|    | 2.1                     | Real-time Systems                        | 10   |  |  |  |  |

|    |                         | 2.1.1 Definitions and Properties         | 10   |  |  |  |  |

|    |                         | Real-Time Tasks                          | 11   |  |  |  |  |

|    |                         | Task Specification                       | 12   |  |  |  |  |

|    |                         | 2.1.2 Worst-Case Execution Time Analysis | 14   |  |  |  |  |

|    |                         | 2.1.3 Real-Time Scheduling               | 16   |  |  |  |  |

|    |                         | 2.1.4 Scheduling Analysis                | 18   |  |  |  |  |

|    | 2.2                     | Mixed-Criticality Systems                | 19   |  |  |  |  |

|    | 2.3                     | Conclusion and Considered System Model   | 20   |  |  |  |  |

|    |                         | 2.3.1 Task Model                         | 20   |  |  |  |  |

|    |                         | 2.3.2 Scheduling Policy                  | 21   |  |  |  |  |

| 3  | Mu                      | i-Core Memory Access Interference        | 23   |  |  |  |  |

|    | 3.1                     | Memory Hierarchy                         | 24   |  |  |  |  |

|    |      | 3.1.1   | Registers                                          | 25 |

|----|------|---------|----------------------------------------------------|----|

|    |      | 3.1.2   | Scratchpad                                         | 25 |

|    |      | 3.1.3   | Caches                                             | 26 |

|    |      | 3.1.4   | Main Memory (DRAM)                                 | 27 |

|    | 3.2  | Memo    | ry Arbitration Schemes                             | 29 |

|    |      | 3.2.1   | Fixed-Priority                                     | 30 |

|    |      | 3.2.2   | First-Come First-Served                            | 30 |

|    |      | 3.2.3   | Round-Robin                                        | 31 |

|    |      | 3.2.4   | Time-Division Multiplexing                         | 32 |

|    |      | 3.2.5   | Budget-Based Arbitration                           | 34 |

|    |      | 3.2.6   | TDM Arbitration and Multi-Criticality Scheduling   | 35 |

|    | 3.3  | Conclu  | usion and Assumed Hardware Architecture            | 36 |

| Π  | C    | ontrib  | ution                                              | 37 |

| 11 | C    | JIIIID  |                                                    | 57 |

| 4  | Prob | olem St | atement and Contribution Summary                   | 39 |

|    | 4.1  | Thesis  | Problem Statement                                  | 39 |

|    |      | 4.1.1   | Criticality-Aware Arbitration Schemes              | 40 |

|    |      | 4.1.2   | Challenges with Time-Division Multiplexing         | 41 |

|    |      | 4.1.3   | Preemption Costs for Regular TDM Arbitration       | 44 |

|    | 4.2  | Contri  | bution Outline                                     | 46 |

| 5  | Dyn  | amic T  | DM-based Arbitration                               | 47 |

|    | 5.1  | Critica | llity Aware TDM-based Arbitration (TDMfs)          | 48 |

|    | 5.2  | Dynar   | nic TDM-based Arbitration Schemes                  | 50 |

|    |      | 5.2.1   | TDMdz: Deadline Driven Arbitration                 | 50 |

|    |      | 5.2.2   | TDMds: Dynamic TDM Arbitration with Slack Counters | 52 |

|    | 5.3  | Decou   | pling Dynamic TDM Arbitration from Slots           | 55 |

|    |      | 5.3.1   | TDMes: Decoupled from TDM slots                    | 55 |

|    |      | 5.3.2   | TDMer: Memory Variability Awareness                | 58 |

|    | 5.4  | Worst-  | Case Behavior                                      | 59 |

|    | 5.5  |         | ments for Dynamic TDM-Based Arbitration Schemes    | 63 |

|    |      | 5.5.1   | Experimental Setup                                 | 63 |

|    |      | 5.5.2   | Results for Dynamic TDM-Based Arbitration Schemes  | 68 |

|    |      | 5.5.3   | Results for Dynamic TDM with Initial Slack         | 71 |

|    |      | 5.5.4   | Results for Varying Memory Access Latencies        | 74 |

|   | 5.6 | Conclusion                                                 | 77 |

|---|-----|------------------------------------------------------------|----|

| 6 | Dyr | namic TDM-based Arbitration Hardware Design                | 79 |

|   | 6.1 | Architecture Overview                                      | 80 |

|   | 6.2 | Arbitration Logic                                          | 81 |

|   |     | 6.2.1 Deadline and Slack Computation                       | 83 |

|   |     | 6.2.2 Update Rules                                         | 84 |

|   | 6.3 | Control Signal Generation                                  | 85 |

|   | 6.4 | Bit-Width Considerations                                   | 86 |

|   | 6.5 | Worst-case Behavior w.r.t. the Hardware Design             | 87 |

|   | 6.6 | Experiments                                                | 93 |

|   |     | 6.6.1 Evaluation Platform                                  | 93 |

|   |     | 6.6.2 Results for Hardware Synthesis                       | 94 |

|   |     | 6.6.3 Results for Dynamic TDM with Round-Robin Arbitration | 96 |

|   |     | 6.6.4 Results for Bit-Width Constrained Slack Counters     | 98 |

|   | 6.7 | Conclusion                                                 | 99 |

| 7 | Mu  | lti-tasks and Preemption Support 10                        | 01 |

|   | 7.1 | Multi-task Preemptive Scheduling Policy                    | 02 |

|   | 7.2 | Preemption Costs for Dynamic TDM-based Arbitration         | 04 |

|   | 7.3 | Arbitration-Aware Preemption Techniques                    | 05 |

|   |     | 7.3.1 Scheduling with Request Waiting (SHDw)               | 06 |

|   |     | 7.3.2 Scheduling with Request Preemption (SHDp)            | 07 |

|   |     | 7.3.3 Scheduling with Criticality Inheritance (SHDi)       | 08 |

|   |     | 7.3.4 Misalignment Delays                                  | 10 |

|   |     | 7.3.5 Response-Time Analysis                               | 11 |

|   | 7.4 | Experiments                                                | 12 |

|   |     | 7.4.1 Experimental Setup                                   | 12 |

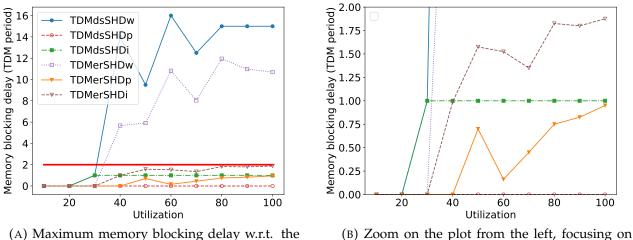

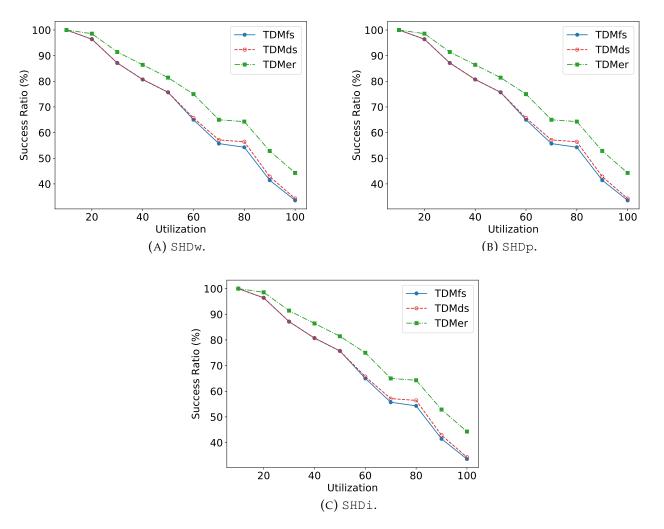

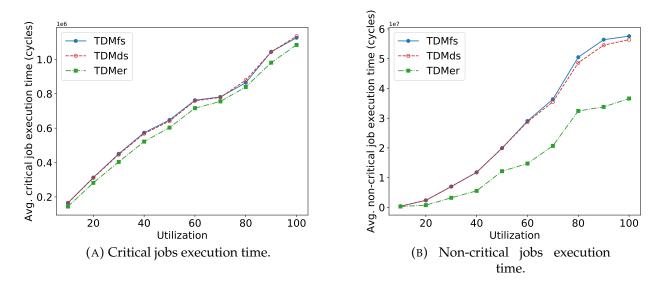

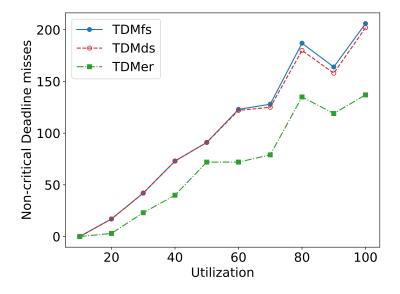

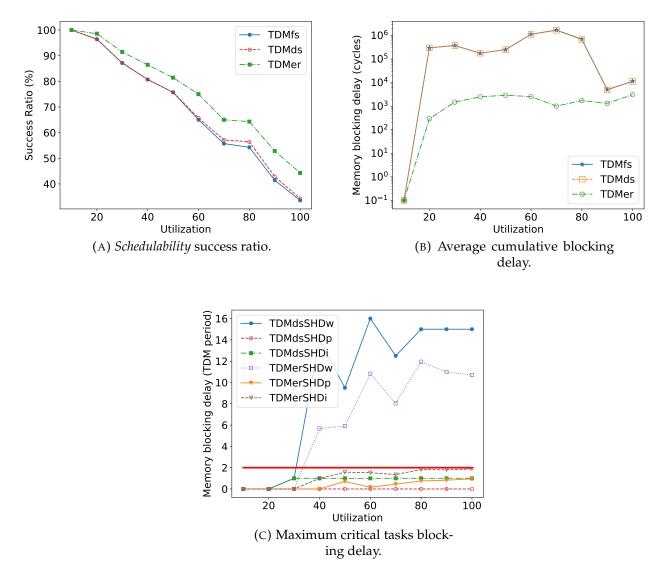

|   |     | 7.4.2 Results for Preemption Schemes                       | 13 |

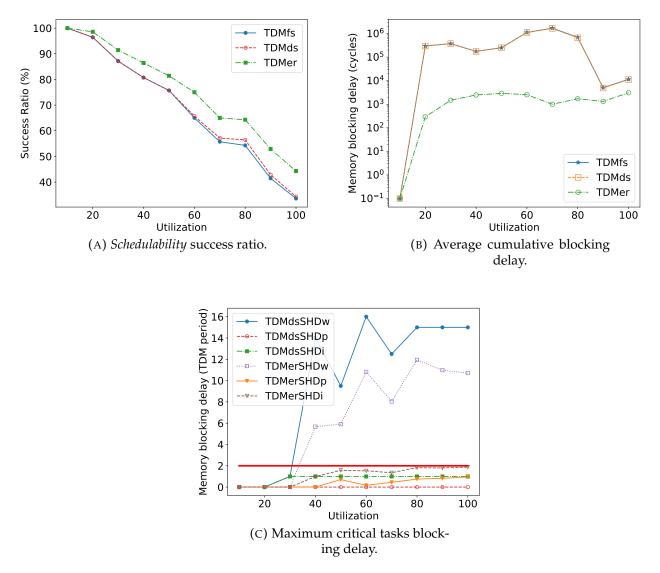

|   |     | 7.4.3 Results for (Preemptive) Arbitration Schemes         | 16 |

|   |     | 7.4.4 Results for Varying Memory Access Latencies          | 19 |

|   | 7.5 | Conclusion                                                 | 21 |

|   |     |                                                            |    |

| Π | ΙΟ  | Conclusion 12                                              | 23 |

125

xiv

|     | graphy       |      |      |      |      |       |      | 129     |

|-----|--------------|------|------|------|------|-------|------|---------|

| 8.2 | Future Work  | <br> | <br> | <br> | <br> |       | <br> | <br>126 |

| 8.1 | Conclusion . | <br> | <br> | <br> | <br> | • • • | <br> | <br>125 |

# **List of Figures**

| 2.1<br>2.2        | Overview of a task specification                                                                                                                                                        | 13<br>15       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 3.1<br>3.2<br>3.3 | Overview of a computer memory hierarchy, figure taken from [26] Overview of a DRAM organization, figure taken from [42]                                                                 | 25<br>28<br>32 |

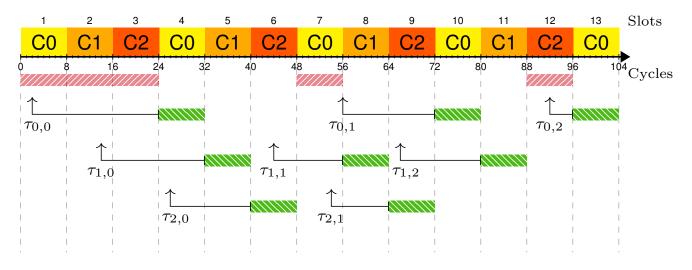

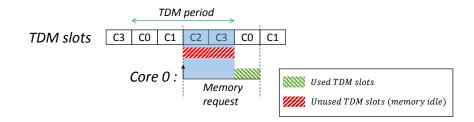

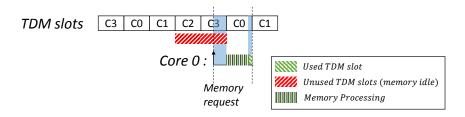

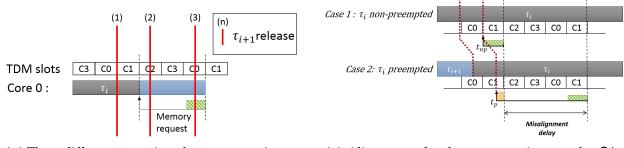

| 4.1<br>4.2<br>4.3 | Non-work-conserving of TDM                                                                                                                                                              | 41<br>42<br>44 |

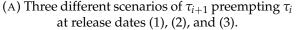

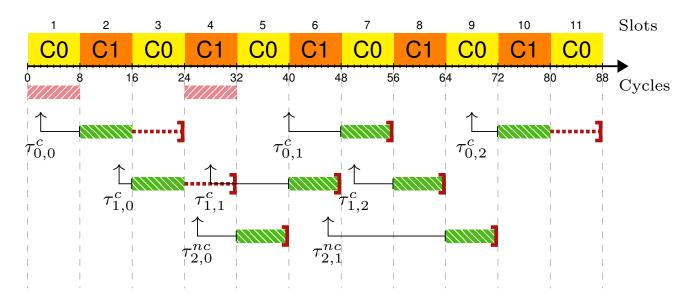

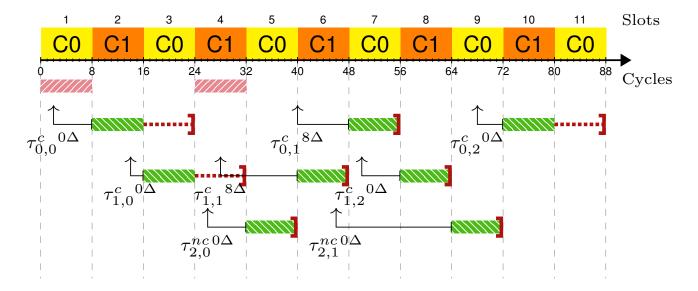

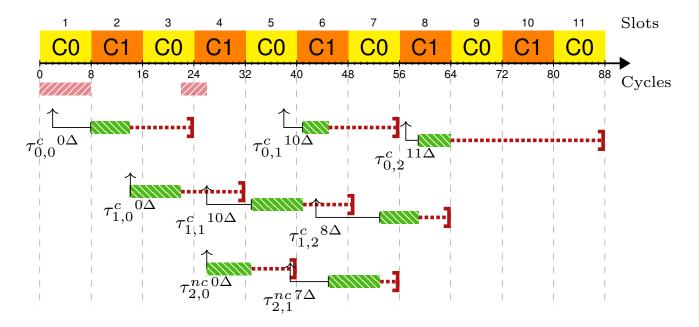

| 5.1<br>5.2<br>5.3 | Criticality aware TDMfs arbitration of three tasks $\tau_0^c$ , $\tau_1^c$ and $\tau_2^{nc}$ Deadline driven TDMdz arbitration of three tasks $\tau_0^c$ , $\tau_1^c$ and $\tau_2^{nc}$ | 49<br>52<br>53 |

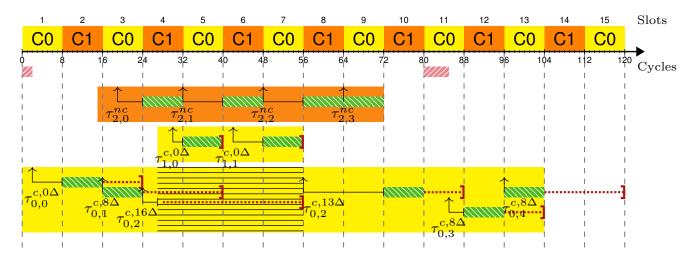

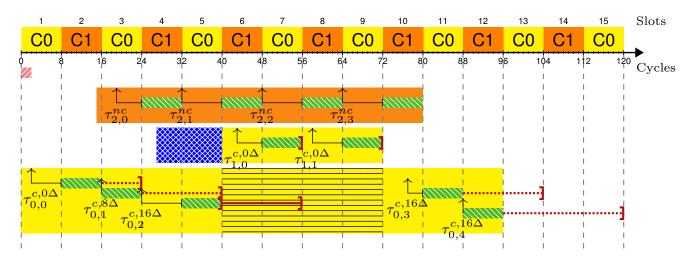

| 5.4               | Reduced issue delays due to the TDMes arbiter, which operates independently from the actual TDM slot length.                                                                            | 57             |

| 5.5               | Elimination of release delays under TDMer arbitration, which considers the actual latency of memory access. Some of the <i>eliminated</i> release delays may simply be                  | 0.             |

| 5.6               | transformed into issue delays                                                                                                                                                           | 58             |

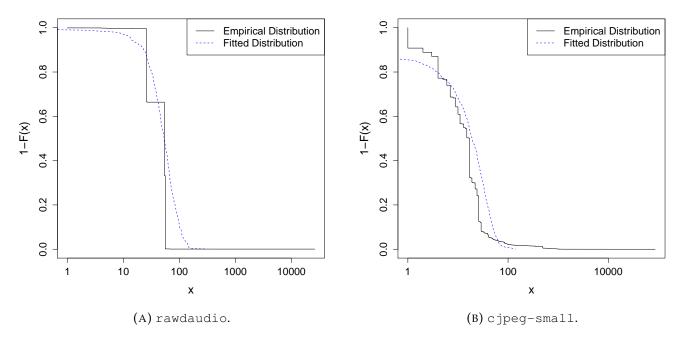

| 5.7               | cations compared with the GEV distributions after fitting                                                                                                                               | 66<br>67       |

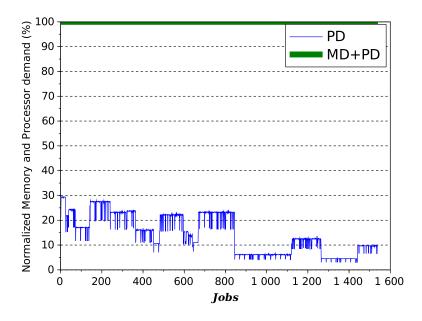

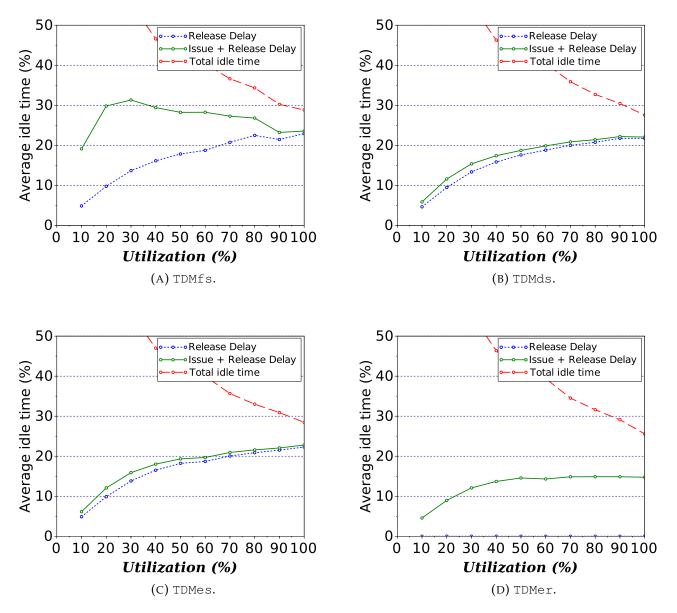

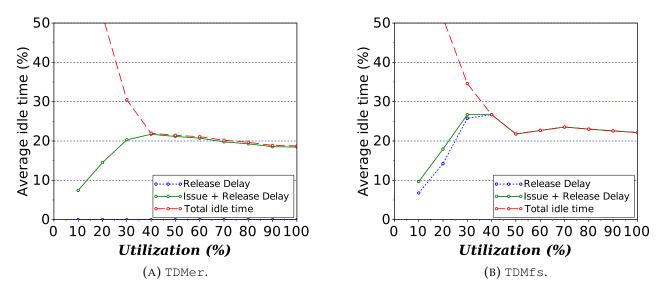

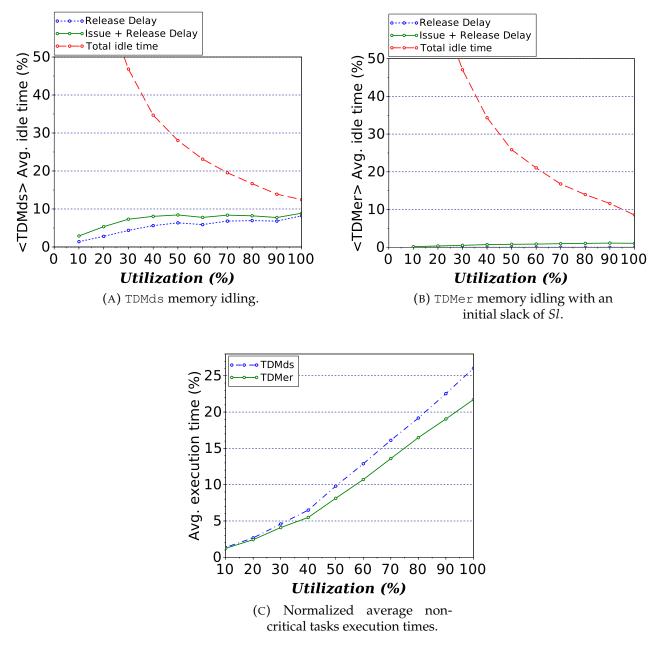

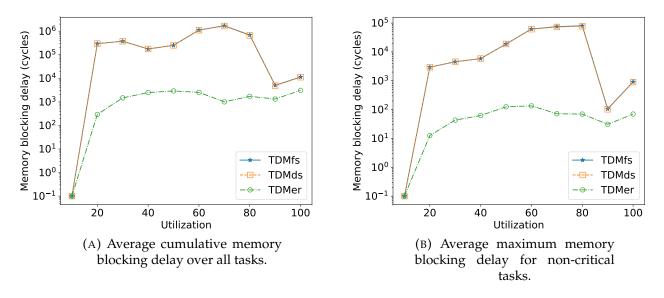

| 5.8               | Evolution of memory idle time, issue, and release delays over all simulations un-<br>der varying utilization (lower is better).                                                         | 69             |

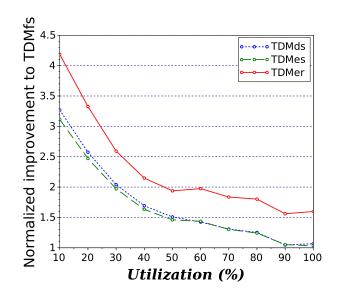

| 5.9               | Normalized sum of issue and release delays for dynamic arbitration schemes com-<br>pared to TDMfs (higher is better).                                                                   | 70             |

| 5.10              |                                                                                                                                                                                         | 71             |

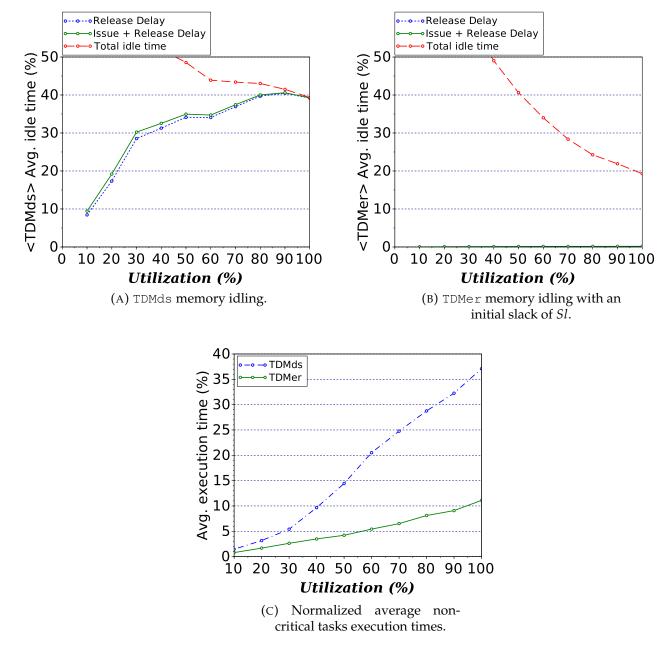

| 5.11                                                                                                   | Evolution of memory idle time, issue, and release delays over all simulations with                                                                                                                                                                                                        |                                               |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|                                                                                                        | varying utilization under TDMer with slack counters initialized to <i>Sl</i> at job start                                                                                                                                                                                                 | 72                                            |

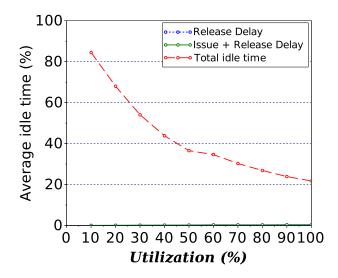

| 5 1 2                                                                                                  | (lower is better)                                                                                                                                                                                                                                                                         | 12                                            |

| 5.12                                                                                                   | under TDMer with initial slack set to <i>Sl</i> (lower is better).                                                                                                                                                                                                                        | 73                                            |

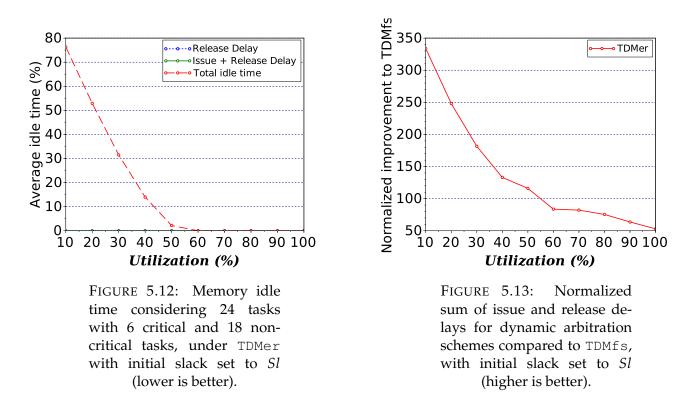

| 5 13                                                                                                   | Normalized sum of issue and release delays for dynamic arbitration schemes com-                                                                                                                                                                                                           | 75                                            |

| 5.15                                                                                                   | pared to TDMfs, with initial slack set to <i>Sl</i> (higher is better).                                                                                                                                                                                                                   | 73                                            |

| 5 14                                                                                                   | Results considering a TDM slot length of $Sl = 25$ cycles (lower is better).                                                                                                                                                                                                              | 75                                            |

|                                                                                                        | Results considering a TDM slot length of $Sl = 20$ cycles (lower is better)                                                                                                                                                                                                               | 76                                            |

| 0.10                                                                                                   | $\frac{1}{10000000000000000000000000000000000$                                                                                                                                                                                                                                            | 70                                            |

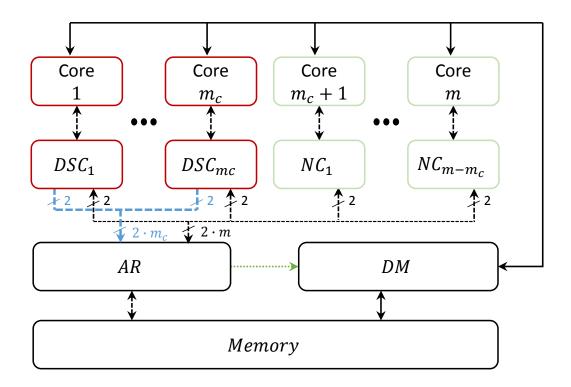

| 6.1                                                                                                    | Overview of the hardware design of our dynamic TDM-based arbiter.                                                                                                                                                                                                                         | 81                                            |

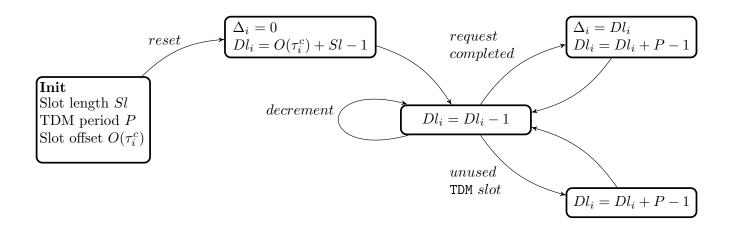

| 6.2                                                                                                    | Summary of the update rules of the Deadline and Slack Computation (DSC) com-                                                                                                                                                                                                              |                                               |

|                                                                                                        | ponents.                                                                                                                                                                                                                                                                                  | 84                                            |

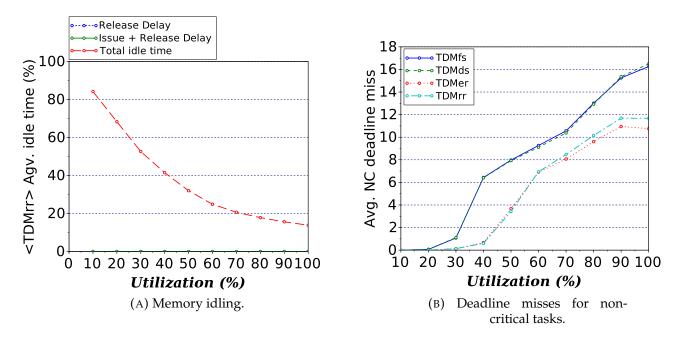

| 6.3                                                                                                    | Evolution of the average memory idling and average number of deadline misses                                                                                                                                                                                                              |                                               |

|                                                                                                        | for non-critical tasks over all simulation runs under TDMrr with initial slack (lower                                                                                                                                                                                                     |                                               |

|                                                                                                        | is better)                                                                                                                                                                                                                                                                                | 97                                            |

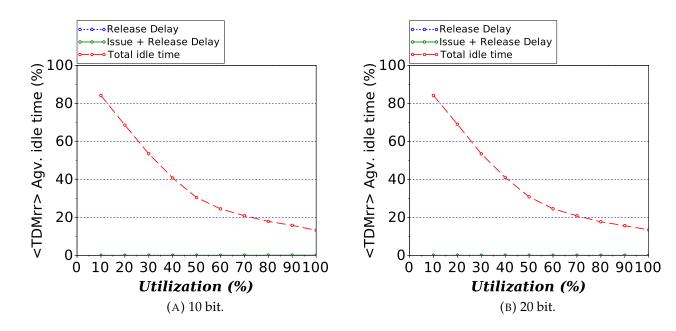

| 6.4                                                                                                    | Evolution of memory idle time considering reduced bit-widths for the slack and                                                                                                                                                                                                            |                                               |

|                                                                                                        | deadline counters under TDMrr with initial slack (lower is better)                                                                                                                                                                                                                        | 99                                            |

| 7.1                                                                                                    | Hardware architecture.                                                                                                                                                                                                                                                                    | 103                                           |

| 7.2                                                                                                    | Impact of slack accumulation on the memory blocking time for TDMds                                                                                                                                                                                                                        | 405                                           |

|                                                                                                        | input of black accumulation of the memory brocking time for ibilability in the                                                                                                                                                                                                            | 105                                           |

| 7.3                                                                                                    |                                                                                                                                                                                                                                                                                           |                                               |

| 7.3<br>7.4                                                                                             | Memory blocking delays considering criticality inheritance (SHDi)                                                                                                                                                                                                                         | 108                                           |

|                                                                                                        | Memory blocking delays considering request preemption (SHDp)                                                                                                                                                                                                                              | 108<br>110                                    |

| 7.4                                                                                                    | Memory blocking delays considering request preemption (SHDp)                                                                                                                                                                                                                              | 108<br>110                                    |

| 7.4<br>7.5                                                                                             | Memory blocking delays considering request preemption (SHDp)                                                                                                                                                                                                                              | 108<br>110<br>113                             |

| 7.4<br>7.5                                                                                             | Memory blocking delays considering request preemption (SHDp) Memory blocking delays considering criticality inheritance (SHDi) Memory blocking delays across normalized system utilization for SHDw Maximum memory blocking delay for critical tasks across normalized system uti-        | 108<br>110<br>113<br>115                      |

| 7.4<br>7.5<br>7.6                                                                                      | Memory blocking delays considering request preemption (SHDp) Memory blocking delays considering criticality inheritance (SHDi) Memory blocking delays across normalized system utilization for SHDw Maximum memory blocking delay for critical tasks across normalized system utilization | 108<br>110<br>113<br>115                      |

| <ol> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> </ol>                                         | Memory blocking delays considering request preemption (SHDp) Memory blocking delays considering criticality inheritance (SHDi) Memory blocking delays across normalized system utilization for SHDw Maximum memory blocking delay for critical tasks across normalized system utilization | 108<br>110<br>113<br>115<br>116               |

| <ol> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> </ol>                                         | Memory blocking delays considering request preemption (SHDp) Memory blocking delays considering criticality inheritance (SHDi) Memory blocking delays across normalized system utilization for SHDw Maximum memory blocking delay for critical tasks across normalized system utilization | 108<br>110<br>113<br>115<br>116<br>117        |

| <ul><li>7.4</li><li>7.5</li><li>7.6</li><li>7.7</li><li>7.8</li></ul>                                  | Memory blocking delays considering request preemption (SHDp)                                                                                                                                                                                                                              | 108<br>110<br>113<br>115<br>116<br>117        |

| <ul> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> <li>7.8</li> <li>7.9</li> </ul>               | Memory blocking delays considering request preemption (SHDp)                                                                                                                                                                                                                              | 108<br>110<br>113<br>115<br>116<br>117<br>118 |

| <ul> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> <li>7.8</li> <li>7.9</li> <li>7.10</li> </ul> | Memory blocking delays considering request preemption (SHDp)                                                                                                                                                                                                                              | 108<br>110<br>113<br>115<br>116<br>117<br>118 |

# **List of Publications and Patents**

### **Publications**

- [HJBP17] Farouk Hebbache, Mathieu Jan, Florian Brandner, and Laurent Pautet, Dynamic Arbitration of Memory Requests with TDM-like Guarantees, In 10th International Workshop on Compositional Theory and Technology for Real-Time Embedded Systems (CRTS 2017).

- [HJBP18a] Farouk Hebbache, Mathieu Jan, Florian Brandner, and Laurent Pautet,

Shedding the Shackles of Time-Division Multiplexing, in 39th (IEEE) Real-Time Systems Symposium, (RTSS 2018).

- [HBJP19a] Farouk Hebbache, Florian Brandner, Mathieu Jan, and Laurent Pautet, Arbitration-Induced Preemption Delays, In 31st Euromicro Conference on Real-Time Systems (ECRTS 2019).

- [HBJP19b] Farouk Hebbache, Florian Brandner, Mathieu Jan, and Laurent Pautet,

Work-conserving dynamic time-division multiplexing for multi-criticality systems, In Special Issue on Addressing the Real-Time Challenges of Multicore Architectures of the *Real-Time Systems* journal, 2019.

### Patent

[HBJP18b] Farouk Hebbache, Florian Brandner, Mathieu Jan, and Laurent Pautet,

Procédé de multiplexage temporel pour l'accès à des ressources partagées,

patent submitted in October 2018. French deposit number 1860117.

### Chapter 1

# Introduction

#### Contents

| 1.1 | Context               | 1 |

|-----|-----------------------|---|

| 1.2 | Contribution Overview | 2 |

| 1.3 | Thesis Outline        | 4 |

### 1.1 Context

A current trend in real-time embedded systems is integrating multiple tasks into a single platform. However, the tasks in domains like avionics and automotive are usually characterized with different importance, safety, or certification requirements – leading to several criticality levels. Running such tasks on a single platform creates a *Multi-Criticality* (MC) system. Hence, integrating such diverse tasks on a single platform requires complete *timing* and *spatial* isolation. This isolation prevents a critical task from being unintentionally affected by another non-critical task. To achieve spatial isolation, i.e., protecting task's state (memory and stored registers), designers usually rely on partitioning mechanisms at the platform level. On the other hand, temporal isolation guarantees a task's desired timing behavior. Achieving temporal isolation is not trivial, especially when considering a multi-core platform with shared resources, such as caches or main memory. This results in challenging issues when trying to tightly bound the tasks' worst-case execution times (WCETs) and avoid over-provisioning hardware resources. For the verification and certification of critical tasks, the most important element is the respect of their timing constraints. For non-critical tasks, however, effectively using the hardware resources is more important than isolation and predictability guarantees as long as critical tasks are not affected.

As mentioned above, multi-core architectures pose many challenges. One main challenge arises from contention between concurrent accesses to shared resources. If several cores access shared memory, for instance, in an uncontrolled manner, interference among tasks of different criticalities cannot be avoided. Then, a non-critical task accessing the memory bus can block the access of any other concurrently executed task. Hence, each access of non-critical tasks can potentially affect the response time of critical tasks on other cores. A way of bounding the interference independently from the concurrent execution of other tasks, is to use temporal isolation [16]. It is possible to achieve temporal isolation on any hardware, but this often leads to over-provisioning of the hardware resources. This means providing more hardware resources then actually needed, which may guarantee a risk-free execution but with an underused platform. Techniques like *Time-Division Multiplexing* (TDM) achieve such a temporal partitioning, concurrent accesses here no longer depend on whether concurrent requests exist or not.

TDM provides predictable behavior and improves composability by bounding access latencies and guaranteeing bandwidth independently from other cores. Systematically considering the worst-case behavior of an arbitration policy with regard to memory accesses in the presence of concurrent requests is too pessimistic, as it leads to low resource utilization at run-time. TDM is rarely used as a bus-arbitration policy in multi-core architectures, since it is not *work-conserving* and therefore causes hardware over-provisioning. The problem arises when the owner of a TDM slot does not (yet) have a memory request ready to be served. Under a strict TDM scheme, this slot cannot be reclaimed by another task (as under Round-Robin arbitration). This problem is further amplified as the number of cores increases, leading to longer TDM schedules. Another source of TDM pessimism stems from the length of TDM slots, expressed in clock cycles, which have to be longer than the worst-case latency of handling memory requests. Memory requests targeting a DRAM memory, however, have highly variable latencies [77], as the temporal behavior of the DRAM depends, for instance, on memory refresh operations or whether the accessed memory page changed. Besides, the access latencies of memory load requests are higher than memory writes, since data must be sent back to the requesting core.

### **1.2 Contribution Overview**

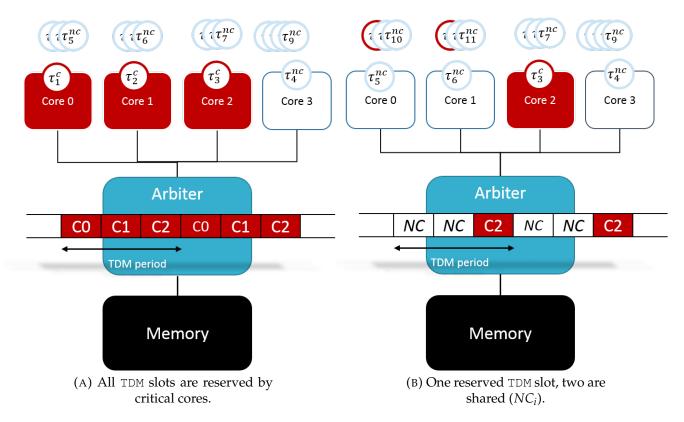

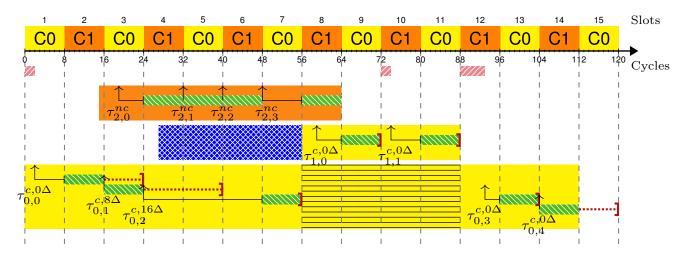

To overcome these aforementioned limitations, we explore the definition of dynamic arbitration schemes based on TDM. We claim that the level of criticality should not only be used by task schedulers, but also by memory arbiters. We thus explore TDM-based arbitration schemes that allow the arbiter, under certain conditions, to favor requests of non-critical tasks over requests from critical tasks. This is achieved by associating deadlines to the memory accesses of critical tasks, which correspond to the end of their corresponding slots under a traditional TDM scheme. These deadlines allow the arbiter to compute the *slack time* (the relative gain compared to an execution under regular TDM) of each pending request from critical tasks in the system. If slack times permit, the arbiter can change the order in which requests are handled by re-allocating slots unused by critical tasks to non-critical tasks. This arbitration policy is called TDMds, for *dynamic TDM with slack counters*, and addresses the source of traditional TDM pessimism. Afterwards, we extend TDMds by proposing two dynamic TDM arbitration schemes (TDMes and TDMer) in order to address the sources of pessimism related to TDM slots. This is achieved by decoupling the arbitration from the TDM slots, i.e., arbitration decisions are at the granularity of clock cycles. Our experiments show that this allows improving delays suffered by traditional TDM by a factor of at least 50, and up to a factor of 300. Another contribution is a formal correctness proof of dynamic TDM-based approaches. Most notably, we prove that TDM's temporal behavior is preserved for critical tasks. Consequently, analysis results valid under TDM, such as offset analyses [41], are equally valid under our schemes.

We also propose a hardware implementation of a variant of our scheme that takes implementation trade-offs and costs into consideration. We show that these trade-offs do not impact the overall performance of our approach while enabling a simple and efficient implementation. A formal proof of the worst-case behaviour for the new approach is also addressed.

The proposed dynamic TDM-based arbitration techniques encounter issues under a preemptive execution model, more precisely, the overhead induced by the arbitration scheme on a preemption. Under our dynamic TDM-based arbitration schemes, tasks may suffer from arbitrationinduced preemption delays. Therefore, we define two memory delays induced by preemptions, the *memory blocking delay* and the *misalignment delay*, which may lead to significant jitter and increase task response times. Even worse, due to non-critical tasks, the memory blocking delay may be unbounded in some circumstances. We explore three different approaches to analyze the impact of these arbitration-induced preemption delays considering preemptive [56] (SHDp) and non-preemptive [6] (SHDw) memory requests. Finally, we propose a new technique (SHDi) to resolve these issues by adapting (priority or rather) *criticality inheritance* known from scheduling theory. This allows us to manage and easily bound these preemption delays. Our evaluation shows that our new approach successfully limits the worst-case preemption delays experienced at runtime under our dynamic TDM-based arbitration schemes. At the same time, we see virtually no impact on average-case performance and success rate. Note, besides, that the proposed technique is not limited to the dynamic TDM-based arbitration schemes and is also applicable to other arbitration techniques, e.g., arbitration based on fixed priorities [6].

### 1.3 Thesis Outline

This thesis is summarized below in terms of its organization and the content of the chapters.

- Chapter 2 presents the basics concepts, definitions, and general properties of real-time systems. This also includes an overview of the Worst-Case Execution Time (WCET) analysis problem, which is an important part of real-time system design. Afterwards a discussion on the different scheduling techniques, used in real-time systems to allocate tasks to the hardware resources, is provided. Finally, this chapter also describes mixed-criticality systems which consist of scheduling tasks with different levels of criticality on the same hardware platform, before concluding with the task model assumed in this thesis.

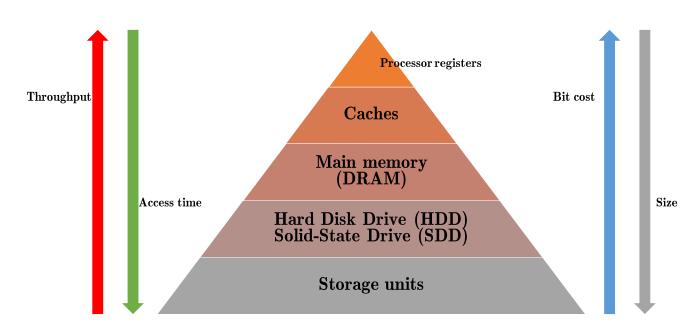

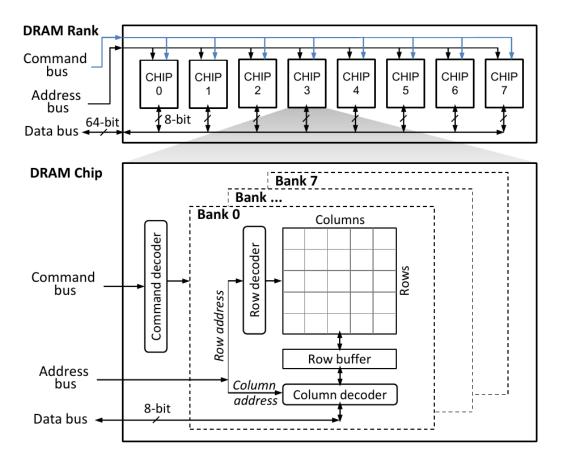

- Chapter 3 focuses on the hardware mechanisms that have an impact on the tasks' worstcase execution time analysis, more precisely on the memory hierarchy. Each of the different levels of the memory hierarchy can have an impact on the WCET of a real-time task. In this thesis, we focus solely on the impact of the arbitration policy that manages shared memory accesses. An overview of the various existing arbitration techniques is provided in this chapter before concluding with a description of the hardware architecture assumed in the context of this thesis.

- Chapter 4 defines the various problems that will be addressed in this thesis, specifically all the aspects that make TDM non-work-conserving.

- Chapter 5 presents our first contributions towards a work-conserving TDM-based arbitrations (TDMds, TDMes, and TDMer already introduced in the previous Section 1.2). This chapter introduces different dynamic criticality-aware TDM-based arbitration schemes, where the arbitration schemes are aware of the tasks' criticalities and take decisions accordingly.

- Chapter 6 presents a simple and efficient hardware implementation of a variant of our proposed arbitration schemes, aiming at reducing the hardware complexity.

- Chapter 7 briefly reviews the dynamic TDM-based arbitration schemes in the context of a preemptive system model. Therefore, we identify the different arbitration-induced preemption delays inherited from TDM and/or specific to our arbitration strategies. In this chapter, we propose various preemption models to handle the arbitration-induces preemption delays and evaluate our contributions using schedulability success ratios and memory utilization.

• Chapter 8 concludes this thesis with a summary of the various contributions and obtained results before finally discussing possible future research perspectives.

# Part I

# Background/State of the art

### Chapter 2

# **Real-Time Systems**

#### Contents

| 2.1 | Real-time Systems    10 |                                      |  |  |  |

|-----|-------------------------|--------------------------------------|--|--|--|

|     | 2.1.1                   | Definitions and Properties           |  |  |  |

|     | 2.1.2                   | Worst-Case Execution Time Analysis   |  |  |  |

|     | 2.1.3                   | Real-Time Scheduling                 |  |  |  |

|     | 2.1.4                   | Scheduling Analysis                  |  |  |  |

| 2.2 | Mixed                   | d-Criticality Systems                |  |  |  |

| 2.3 | Concl                   | usion and Considered System Model 20 |  |  |  |

|     | 2.3.1                   | Task Model         20                |  |  |  |

|     | 2.3.2                   | Scheduling Policy                    |  |  |  |

In this chapter, we are interested in defining real-time systems and the different properties underlying these types of systems. a real-time system is composed of an execution platform (computer system) and tasks running on the execution platform with temporal constraints imposed by the physical environment. Section 2.1 introduces basic concepts, definitions and general properties of real-time systems. This section also includes an overview of the Worst-Case Execution Time (WCET) analysis, which aims to provide upper-bounds for the tasks running on the computer system. The WCET analysis is an important part of real-time system design. After establishing the WCET of the real-time tasks, a scheduling policy is used to allocate the different tasks to the hardware platform on which they will run. Various real-time scheduling techniques are also covered in Section 2.1. In a real-time system, tasks may have different levels of critical-ity depending on the impact that a failure would have on the system and its environment. An overview of mixed-criticality scheduling is provided in Section 2.2, which consist of scheduling

tasks with different criticality levels on the same platform. Finally, as a conclusion, we describe the task model and scheduling policy considered in the context of this thesis in Section 2.3.

### 2.1 Real-time Systems

Real-time systems have applications in many fields of activity, such as transportation, telecommunication, robotics, space missions, multimedia systems, and industry. A real-time system is a *reactive system* in nature. It is often seen as a control environment that is associated with a computer control system. More precisely, a real-time system is in permanent interaction with its external environment, usually represented by a physical process, in order to control its behavior evolving over time. The interactions of a real-time system with its environment are designed in order to respond to events in the controller environment. More precisely, the system response time must be within a limited time, i.e., the system must be able to respond to changes in the state of its environment within this time limit. Not respecting the timing constraints of a realtime system could cause the system to behave incorrectly, causing instability, which could lead to a major system failure.

#### 2.1.1 Definitions and Properties

**Definition 2.1.1.** *Real-Time System* [62, 64]. A *real-time system* is defined as a control-command system in which the application's correctness depends not only on the result but also on the time at which this result is produced. If the application timing constraints are not respected, we talk about system failure.

In a real-time system, *time* is the most important resource to manage. Tasks must be assigned and executed in such a way that they respect their timing constraints. Interactions between tasks are also time-constrained, messages are transmitted in a well-defined time interval between two real-time tasks. The environment in which a computer operates is an essential component of any real-time system. Therefore, the respect of the timing constraints of a real-time system affects its *reliability*. A failure of a real-time system can have catastrophic consequences, whether it is economic or human.

**Definition 2.1.2.** *Predictability* [62, 3]. *A system is considered predictable if a useful bound is known on temporal behavior that covers all possible initial states and state transitions.*

*Predictability* [62] in a real-time system depends on several factors, covering both software and hardware. In a predictable system, it must be possible to determine in advance whether all computation activities can be performed within a given time limit. To this end, the system should be *deterministic*, i.e., based on a sequence of input events, the system produces a sequence of output events, always the same output with the same input and in an order determined by the order of the input events [3]. Several factors affect the deterministic behavior of a system, including its hardware architecture, operating system and the programming language used to write the application.

**Definition 2.1.3.** *Composability* [3, 4]. A system is considered composable if tasks cannot affect the behavior of any other task, neither its computation result nor its temporal behavior.

In a composable system, a component of the system should not affect the temporal behaviour of another component unintentionally [9]. *Composability* is a major factor in improving the predictability of the system. However, modern hardware architectures include several advanced functions (e.g. caches), which increase the average performance of the system at the cost of highly variable timing behaviour. Since these hardware resources are most often shared and are based on historical execution information to improve performance, the execution time of an application is likely to depend on the execution history and interference of other competing applications.

#### **Real-Time Tasks**

**Definition 2.1.4.** *Real-Time Task* [62, 64, 8]. *A real-time task denoted*  $\tau_i$ , *sometimes also called a process or a thread, is an executable entity of work which, at a minimum, is characterized by a worst-case execution time and a time constraint.*

**Definition 2.1.5.** *Job* [64, 8]. *A job is a running instance of a task on the hardware platform.*

Tasks in a real-time system are invoked/activated at regular intervals and must be executed in a limited time window. Each invocation of a task corresponds to a job that monitors the state of the system by taking input data, performs some computations and, if necessary, sends commands to modify and/or display the state of the system. A real-time task is often characterized by its criticality level, which is defined according to the severity that a task failure will have on its environment. A real-time task is also characterized by its temporal properties, distinguishing several types of task: periodic, aperiodic and sporadic. Each type normally gives rise to multiple jobs.

**Definition 2.1.6.** Periodic Tasks [64, 49, 73]. Periodic tasks are real-time tasks which are activated (released) regularly at fixed rates (period). The period of a task  $\tau_i$  is commonly designated by  $T_i$ . The time constraint for an instance of a periodic task is a deadline  $d_i$  that can be less than, equal to, or greater than the period. It is often assumed that the deadline equals the period (implicit deadline).

Generally, a periodic task is used for the acquisition or the production of data at regular times. The task activities must be performed in a cyclically manner at specific rates, which can be derived from the requirements of the application. For instance, this type of task is used for monitoring purposes, where the task acquires data from sensors at regular intervals. The utilization denoted  $u_i$ , of a periodic task  $\tau_i$  is the ratio of its execution time  $C_i$  over its period  $\tau_i$ , i.e.,  $u_i = \frac{C_i}{T_i}$ .

**Definition 2.1.7.** Aperiodic Tasks [64, 73]. Aperiodic tasks are real-time tasks which are activated irregularly at some unknown and possibly unbounded rate. Aperiodic tasks have soft deadlines or no deadlines.

Aperiodic tasks are event-driven, which means that these tasks behave in an unpredictable way and are governed by events from the system environment.

**Definition 2.1.8.** Sporadic Tasks [64, 73]. Sporadic tasks are real-time tasks which are activated irregularly with some known bounded rate. The bounded rate is characterized by a minimum inter-arrival period, that is, a minimum interval of time between two successive activations. This is necessary (and achieved by some form of flow control) to bound the workload generated by such tasks. The time constraint is usually a deadline  $d_i$ .

Just like aperiodic tasks, sporadic tasks are event-driven. There is no prior knowledge of the arrival times of sporadic tasks. However, they do have requirements on the task's minimum inter-arrival time. Unlike aperiodic tasks that may not have hard deadlines, sporadic tasks do have hard deadlines, i.e. when the triggering event of the task occurs, a response is required in a limited time window.

#### **Task Specification**

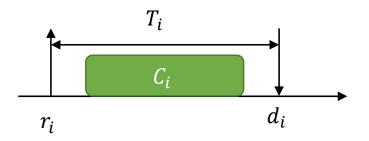

In real-time systems, a task  $\tau_i$  is characterized, as depicted in Figure 2.1, by its priority  $\prod_i$ , its release time  $r_i$ , its deadline  $d_i$ , its execution time  $C_i$ , and its period  $T_i$ .

**Definition 2.1.9.** *Release Time* [64, 73]. *A release time*  $r_i$ , *is a point in time at which a real-time job becomes ready to (or is activated to) execute.*

FIGURE 2.1: Overview of a task specification.

A job can be scheduled for execution at any time at or after the release time. It may or may not be executed immediately, because, for example, a higher or equal-priority task is using the processor.

**Definition 2.1.10.** *Deadline* [64, 8]. *A deadline*,  $d_i$  *is a point in time by which the task (job) must complete.*

Usually, a deadline  $d_i$  is an *absolute time*. Sometimes,  $d_i$  is also used to refer to a *relative deadline*. To avoid confusion we denote the relative deadline as  $D_i$ . A relative deadline of a task is the deadline measured in reference to its release time.

**Definition 2.1.11.** *Priority* [64]. *The priority i of a task indicates its order of importance for scheduling.*

A task has a priority  $\prod_i$ , which can be fixed or dynamically assigned. The higher the value of a task, the higher this task's priority level. Most of the time, the highest priority task instance (job) that is ready, i.e., whose activation/release date has passed and that has not yet completed, is elected to be executed by the processor. Note that in this thesis, we assume fixed priority assignment, hence the index of task *i* is equal to its priority  $\prod_i$ . Therefore, the task index *i* also represents its priority.

**Definition 2.1.12.** *Execution Time. A task's execution time is the required time for a processor to execute an instance, i.e., job, of a task*  $\tau_i$ .

The execution time  $C_i$  of a task is not always constant (see Section 2.1.2). For example, a task can have different execution paths and different number of loop iterations each time the task executes. The execution paths and the number of loop iterations vary because of the changes in the input data. The upper-bound and lower-bound of a task's execution time are defined as follows:

**Definition 2.1.13.** Worst-Case Execution Time (WCET) [76]. The WCET represents the longest execution time of any job of a task under any circumstances.

**Definition 2.1.14.** *Best-Case Execution Time* (BCET) [76]. *The BCET represents the shortest execution time of any job of a task under any circumstances.*

When designing a system following the multi-tasking approach (several tasks sharing the same hardware execution platform), in addition to execution times, one has to consider the response-time  $R_i$  of a task.

**Definition 2.1.15.** *Response Time. The response time of a task corresponds to the interval from the task's release time to the task's completion.*

In a multi-tasking scheduling context, a task is not executed immediately when it is released because the required shared resources or the processor may be used by higher priority tasks and might thus not be available. Besides, in a preemptive scheduling context, a lower priority task can be suspended so that the processor can execute a higher priority task which is ready. As a result, a task's response time could be larger than its execution time.

#### 2.1.2 Worst-Case Execution Time Analysis

A real-time system must be valid not only with regard to the computed results but also with regard to its time constraints. This assessment is based on bounding the temporal behavior of every task in the system. Specifically, a task's worst-case execution time (WCET) is used to ensure that its deadline is met in all cases, even in the worst case.

The task's execution time is not constant and varies according to many factors [22] that can be divided into two parts, (1) *hardware*, the architectural mechanisms implemented at the processor level, and (2) *software*, the operating system and concurrent tasks, including program inputs that can affect the path followed in the task. Many research studies have focused on obtaining an upper-bound of the worst-case execution time in the context of complex single-core architectures. This interest in obtaining a reliable and accurate upper-bound is driven by the criticality of real-time systems where a system failure can lead to severe consequences, and the cost of pessimism and imprecision during system validation, leading to low hardware resource utilization.

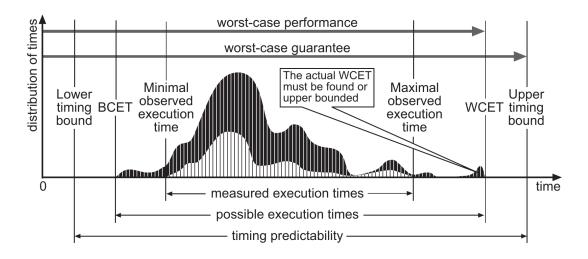

FIGURE 2.2: Task execution time distribution, figure taken from [76].

As mentioned before, WCET analysis relies on the hardware platform on which the task's jobs are running. The increase in the complexity of hardware architectures meets the performance needs of general-purpose systems, which also applies to real-time systems, albeit to a lesser extent. Hardware solutions have the benefit of being transparent to the users of the systems involved. However, more complex architectures are usually difficult to analyse, due to the large state space. Either we explore this large state space (good precisions, bad analysis time) or we use abstractions to simplify the analysis (better analysis time with less precision).

Figure 2.2 illustrates the difference between best-case, worst-case, and average execution time of a given task. The set of all execution times is shown as the upper curve, along with the bestand worst-case execution times (BCET and WCET). In most cases, the state space is too large to exhaustively explore all possible executions and thereby determine the exact worst- and best-case execution times.

There are three main families of methods for bounding the worst-case execution time of a task [76]:

**Dynamic or measurement-based methods:** The common method to establish execution-time bounds is to measure the *end-to-end* execution time of the task for a subset of the possible executions. For this method, the task, or parts of it, execute on the given hardware or a simulator for some set of inputs. From measured times the maximal and minimal observed execution times are derived. In general, these methods overestimate the BCET and underestimate the WCET and

so are not safe for hard real-time systems. A safety margin is thus often added to the observed maximal execution time, e.g., by multiplying by a given factor – the resulting WCET estimate may still be unsafe.

**Static methods:** To compute the execution time bounds of a task, static methods are not based on any execution but on the observation and analysis of its source code or binary code. This method analyze the set of all possible execution paths through the (binary) code of a task, combines this information with an abstract model of the hardware architecture, and obtains an upper bound for this combination [75]. Since all analysis steps aim to compute over-approximations, the obtained bounds are safe. However, it is challenging to proof that the formal analysis models actually match the underlying hardware implementations (which might not be publicly available, contain bugs, be poorly documented, or not be documented at all).

**Probabilistic methods:** Probabilistic analyses build upon the fact that an exhaustive measurement of the WCET cannot be made for all possible states of the system, and that hardware architectures are so complex that static analysis is often very difficult to perform. Burns et al. [17] proposed a statistical method, where execution time is represented by a probabilistic function. The WCET upper-bound is associated with a confidence level by which the upper-bound can be held. Therefore, the probabilistic WCET (pWCET) is defined as follows [23]: *The probabilistic worst-case execution time (pWCET) of a task describes the probability that the worst-case execution time of that task does not exceed a given value.* Probabilistic methods often require special properties on the software and hardware (e.g., independence of execution times) and are still subject to research.

### 2.1.3 Real-Time Scheduling

In a system with multiple resources that can be accessed simultaneously by multiple users, it is necessary to assign the available resources to the task to be executed, according to a *scheduling policy*. The scheduler is responsible for allocating tasks to processors and managing contention within each processor. In the case of real-time systems, the scheduler has to guarantee the respect of a task's timing constraints. In other words, all tasks must meet their deadlines.

There are two categories of real-time scheduling strategies: static and dynamic [21].

**Static scheduling** is based on an *off-line* definition of a static table, containing a sequence of all scheduling decisions regarding the task's executions. The definition of the static table requires prior knowledge of a task's behavior. This scheduling type can be applied to time-driven tasks

(e.g. periodic tasks) which offers a predictable temporal behavior. Another interesting point of static scheduling is its low runtime overhead. However, this scheduling strategy remains very inflexible, with regard to changes in the environment during execution, since it assumes that all parameters, including the release dates, have been fixed in advance.

**Dynamic scheduling** is an *online* approach of a task to processor allocation. The decisions are based on the current state of the system and the properties of the ready tasks, i.e., according to the task's timing constraints at runtime. This approach offers a more flexible scheduling strategy that can handle even-triggered tasks, therefore offering a higher processor utilization. However, such an approach can have high runtime cost and can be very complex to implement.

Different dynamic scheduling policies exist which mainly reside in two classes of algorithms [14]:

**Fixed-priority scheduling algorithms:** This approach considers that each task is assigned a priority a priori. The scheduling is done so that the task with the highest priority is assigned to the processor. The task priority can be set according to various criteria, for example, the *Rate Monotonic Scheduling* (RMS) [74, 49] policy gives the highest priority to the task with the shortest period. Another example, under *Deadline Monotonic Scheduling* (DMS) [74] where this time the task priority is assigned according to a task's deadline.

**Dynamic-priority scheduling algorithms:** As with fixed-priority scheduling, the scheduling decision relies on task priorities. The difference here is that the priorities dynamically change during runtime, according to various criteria. The best-known approach, *Earliest Deadline First* (EDF) [74] policy, is based on the relative deadline of the tasks. The EDF policy consists in assigning the highest priority to task with the lowest relative deadline, i.e., the smallest difference between the task absolute deadline and the current date. *Least Laxity First* (LLF) [36] is another dynamic priority approach where the priority varies according to the difference between the remaining execution time of the task instance and its relative deadline: the lower the difference is, the higher is the task priority.

Real-time scheduling may be *preemptive* or *non-preemptive*. Using a preemptive scheduling strategy, the execution of a task can be interrupted at any time by the scheduler in favor of a higher priority task. The preempted task resumes its execution after the completion of the higher priority task. On the other hand, non-preemptive scheduling does not allow task interruption.

### 2.1.4 Scheduling Analysis

The validation of a real-time system is based on its temporal aspect, which consists of verifying that all the jobs will always respect their deadlines. To do so, a given task set denoted  $\Gamma$  is analyzed and tested for *feasibility* and *schedulability* depending on the scheduling policy:

**Definition 2.1.16.** *Feasibility* [8, 68]. *Feasibility is the assessment of the ability to satisfy all timing constraints of a task set.*

**Definition 2.1.17.** *Feasible* [8, 68]. *A task set is feasible if there exists a scheduling policy guaranteeing that all timing constraints are met.*

A real-time task generates a sequence of jobs, each job has a deadline. If all instances (jobs) of the task set can be scheduled with all their deadlines met, then the task set is said to be feasible.

**Definition 2.1.18.** *Schedulability* [8, 68]. *Schedulability is the assessment of the feasibility of a task set under a given scheduling policy.*

**Definition 2.1.19.** *Schedulable* [8, 68]. *A task set is schedulable under a scheduling policy if none of its tasks, during execution, will ever miss their deadlines.*

Schedulability tests are based on the temporal characteristics of the task set. These tests verify several conditions in order to assess the schedulability of a task set. These conditions may be necessary, sufficient or exact [68] and depend on the characteristics of the systems under which they are applied.

There are three main classes of schedulability tests:

**Processor utilization:** The processor utilization factor relies on the ratio between the *n* tasks' execution times and their periods, which is computed as follow:

$$U = \sum_{i=1}^{n} \frac{C_i}{T_i}$$

For example, this test can be applied to the RM preemptive scheduling policy, the test is considered sufficient but not necessary [49], as long as the processor utilization does not exceed  $n \cdot (\sqrt[n]{2} - 1)$ . Different bounds can be found for different scheduling approaches (DM, EDF, LLF), these bounds and their conditions also depend on the environment and the type of the considered system. For example, in a distributed system of dependent tasks, the conditions determined by the processor utilization factor remain necessary and not sufficient.

**Processor demand:** This test is based on the computation of cumulative demand of task executions. It involves testing for any time interval  $[t_1, t_2]$ , that the maximum cumulated tasks' execution times, released and ended execution in this interval, does not exceed the length of the interval [49].

**Response-time:** This test is based on the tasks' Worst-Case Response Times (WCRTs) computation. It can be applied to any variant of Fixed-Priority scheduling techniques. This approach is therefore based on worst-case scenario analysis rather than on an exhaustive exploration of all possible states. In addition, this approach can be applied to more complex systems such as systems with random deadlines or dependent tasks, or distributed systems.

The test is sufficient and necessary for task sets that consist of synchronous periodic tasks. For a given task set, the computation of the WCRT,  $R_i$  of a task  $\tau_i$ , is performed using the following recurrence equation [39, 7]:

$$R_i^{n+1} = C_i + B_i + \sum_{\forall j \in hp(i)} \left\lceil \frac{R_i^n}{T_j} \right\rceil C_j$$

(2.1)

The recurrence equations are initialized to  $R_i^0 = 0$  and then iteratively reevaluated until a fixed point is reached.  $R_i$  then indicates the response time of task *i*, having a WCET bound  $C_i$ . In addition, the impact of preemptions by tasks with higher priority than i ( $j \in hp(i)$ ) is considered via their WCET bounds  $C_j$  and periods  $T_j$ .  $B_i$  indicates an upper bound on the time task *i* may be blocked (e.g., by semaphores). If all tasks meet their deadlines (i.e.  $\forall i : R_i \leq D_i$ ) than the corresponding task set is schedulable.

## 2.2 Mixed-Criticality Systems

Several factors make the computation of an upper-bound for the worst-case execution time complex and most often result in a very pessimistic upper-bound. The schedulability tests are based on these pessimistic WCETs and result in low processor utilization, hence an inefficient use of the underlying hardware resources. Some approaches have been developed to take advantage of this pessimism. Vestal [71] has introduced the so-called mixed-criticality systems, where different criticality tasks are scheduled on the same platform with properties that take advantage of the WCET pessimism.

In a mixed-criticality system, a task  $\tau_i$  is characterized [18] by a criticality level  $L_i$ , a set of worst-case execution times  $(C_i(1), C_i(2), ..., C_i(L_i))$  depending on the criticality level, a deadline  $(D_i)$  and a period  $(T_i)$ . The scheduling of a task set  $\Gamma$  under a mixed-criticality system relies on the *execution mode* X. This mode is related to the criticality level in which the system is operating, such that it only allows tasks with a higher criticality level to be executed, i.e.  $L_i \ge X$ . A mode change is triggered every time a TFE (*Timing-Failure Event*) occurs. The TFE refers to the case where a running job reaches its  $C_i(X)$  and therefore it will be granted a higher worst-case execution time  $C_i(X + 1)$  so that it can finish executing at the cost of stopping lower criticality jobs. In a two-level criticality model ( $\forall \tau_i \in \Gamma, L_i \in [1, 2]$ ), the two execution modes work as follows:

- Low mode (X = 1): supports the execution of all tasks with criticality levels  $L_i \in [1, 2]$ .

- High mode (X = 2): only enables tasks with a criticality level  $L_i = 2$  to be executed.