# Wideband Analog-to-Digital Converter (ADC) design for power amplifiers linearization

Kelly Tchambake Yapti

#### ▶ To cite this version:

Kelly Tchambake Yapti. Wideband Analog-to-Digital Converter (ADC) design for power amplifiers linearization. Electronics. Université Paris Saclay (COmUE), 2019. English. NNT: 2019SACLT047 . tel-03279780

# HAL Id: tel-03279780 https://pastel.hal.science/tel-03279780

Submitted on 6 Jul 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Wideband Analog-to-Digital Converter Design For Power Amplifiers Linearization

Thèse de doctorat de l'Université Paris-Saclay préparée à Télécom Paris

Ecole doctorale n°580 Sciences et Technologies de l'information et de la Communication (STIC)

Spécialité de doctorat : Réseaux, Information et Communications

Thèse présentée et soutenue à Paris, le 30 Août 2019, par

# KELLY TCHAMBAKE

#### Composition du Jury:

Dominique Dallet

Professeur, Université de Bordeaux Rapporteur

Marie-Minerve Louërat

Chargée de Recherche HDR, CNRS-Sorbonne Université Rapporteur

Hervé Barthémély

Professeur, Université de Toulon Examinateur

Caroline Lelandais-Perrault

Maître de Conférence, Centrale-Supéllec Examinateur

Patricia Desgreys

Professeur, Télécom Paris Directeur de thèse

Chadi Jabbour

Maître de Conférence, Télécom Paris Co-directeur de thèse

Dang-Kièn Pham

Ingénieur de Recherche, Télécom Paris Invité

# Résumé

De nos jours, la consommation d'énergie devient un des principaux défis à surmonter dans le développement des réseaux de communications mobiles. L'amplificateur de puissance est le composant le plus gourmand en consommation d'énergie dans les stations de base. L'arrivée de la cinquième génération de téléphonie mobile avec ses bandes de communication plus larges et ses modulations complexes augmente encore plus les contraintes sur l'amplificateur de puissance. Pour palier ce problème, il est courant de faire appel à des techniques de pré-distorsion qui permettent de faire fonctionner l'amplificateur de puissance avec un meilleur rendement énergétique. Une contrainte importante dans la mise en oeuvre de cette technique est la numérisation de la sortie de l'amplificateur qui, dû aux non-linéarités, s'étale sur un spectre significativement plus large que le signal utile, environ 5 fois en pratique voire plus.

Habituellement, pour cette opération de numérisation, un Convertisseur Analogique Numérique (CAN) du type pipeline est utilisé car il permet d'obtenir des résolutions supérieures à 10 bits sur une bande de plusieurs dizaines voire centaines de MHz. Cependant, sa consommation d'énergie élevée pousse à explorer d'autres pistes. L'architecture "Multi Stage Noise Band Cancellation" (MSNBC) à base de modulateurs Delta Sigma a l'avantage de réaliser des dynamiques différentes par sous bande et est ainsi un candidat de choix pour le CAN de la boucle de retour des techniques de pré-distortion.

L'objectif de ce travail est de démontrer la faisabilité de l'architecture MSNBC qui jusqu'à présent a été uniquement étudiée au niveau système. Pour atteindre cet objectif, plusieurs études ont été menées sur des aspects spécifiques de cette architecture tels que l'implémentation de l'annulation du signal primaire à l'entrée des modulateurs secondaires et l'impact du retard de boucle sur sa qualité, le choix de la fréquence centrale des modulateurs primaire et secondaires, et la conception des filtres numériques pour l'annulation du bruit de quantification.

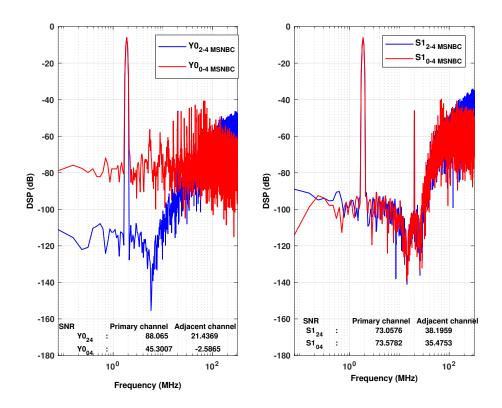

Ces études nous ont permis de proposer une architecture adaptée pour la numérisation d'un signal de bande RF 20 MHz avec des résolutions différentes par sous bande. Une architecture Zéro-IF temps continu avec un modulateur primaire du second ordre et un modulateur secondaire du quatrième ordre avec des quantificateurs 4 bits a été adoptée. Cette architecture a été implémentée en une technologie CMOS 65 nm. Les simulations électrique du MSNBC 2-4 avec un signal LTE ont permis d'obtenir 84.5 dB de SNDR dans la bande principale et 29.2 dB dans la bande adjacente contenant les produits d'intermodulation.

# Abstract

Power consumption is nowadays one of the main challenges to overcome in the development of mobile communications networks. The power amplifier (PA) is the most power hungry component in base transceiver stations. The upcoming fifth generation of mobile telephony with wider communication bands and complex modulations further increases the constraints on the PA. To overcome this problem, it is common to use pre-distortion techniques that enable the power amplifier to operate with greater linearity and efficiency. An important constraint in the implementation of this technique is the digitization of the output of the amplifier which, due to non-linearities, spreads over a significantly wider spectrum than the initial signal, about 5 times in practice or even more.

Pipeline Analog-to-Digital Converters (ADCs) are commonly used for this operation because it allows resolutions of greater than 10 bits to be obtained over a band of several tens or even hundreds of MHz. However, its high energy consumption pushes to find a better solution. The "Multi Stage Noise Band Cancellation" (MSNBC) architecture based on Delta Sigma modulators has the advantage of realizing different dynamics per subband and is thus a prime candidate for the feedback loop ADC of predistortion techniques.

The purpose of this work is to demonstrate the feasibility of the MSNBC architecture that has so far only been studied at the system level. To achieve this objective, several studies have been carried out on specific aspects of this architecture. This includes the implementation of the cancellation of the primary signal at the input of the secondary modulators and the impact of the loop delay on its quality, the choice of the center frequency of the primary and secondary modulators, and the design of the digital filters for quantization noise cancellation.

Our investigations allowed us to propose a suitable architecture to digitize a 20 MHz RF band signal with different resolutions per subband. A continuous time Zero-IF architecture with a second-order primary modulator and a fourth-order secondary modulator with 4-bit quantizers was adopted. This architecture has been implemented in a 65 nm CMOS technology. Transistor level simulations of the

2--4 MSNBC architecture simulations with an LTE test signal resulted in  $84.5~\mathrm{dB}$  SNDR in the main band and  $29.2~\mathrm{dB}$  in the adjacent band which contains the intermodulation products.

# Contents

| R  | ésum   | é      |                                                                                                 | 3  |

|----|--------|--------|-------------------------------------------------------------------------------------------------|----|

| A  | bstra  | .ct    |                                                                                                 | 5  |

| Li | st of  | Abbro  | eviations                                                                                       | 9  |

| In | ıtrodı | uction |                                                                                                 | 13 |

| Ι  | From   | m DP   | D to ADC Specifications                                                                         | 17 |

|    | I.1    | Power  | $^{	ext{Amplifier}}$                                                                            | 17 |

|    |        | I.1.1  | State-of-the-Art of PAs Used in BTS                                                             | 18 |

|    |        | I.1.2  | Linearization Techniques                                                                        | 22 |

|    | I.2    | Digita | l Predistortion Technique                                                                       | 23 |

|    |        | I.2.1  | DPD Implementation                                                                              | 23 |

|    |        | I.2.2  | ADC Implementation Trade-offs                                                                   | 25 |

|    | I.3    | ADC    | Specifications for DPD                                                                          | 27 |

|    |        | I.3.1  | $\label{eq:mixer_substitute} \mbox{Mixer I/Q Imbalance} \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ | 27 |

|    |        | I.3.2  | Fullband Nonlinear Feedback Path                                                                | 28 |

|    |        | I.3.3  | Subband ADC Requirements                                                                        | 29 |

|    | I.4    | Concl  | usion                                                                                           | 31 |

| II | Ana    | dog-to | -Digital Converters State-Of-The-Art                                                            | 33 |

|    | II.1   | A/D    | Conversion                                                                                      | 33 |

|    |        | II.1.1 | Sampling and Quantization                                                                       | 33 |

|    |        | II.1.2 | Performance Metrics                                                                             | 37 |

|    |        | II.1.3 | ADC Architectures                                                                               | 39 |

|    | II.2   | Basics | s of $\Sigma\Delta$ ADCs                                                                        | 41 |

|    |        | II.2.1 | Design Parameters                                                                               | 46 |

|    |        | II.2.2 | NTF Implementation: Continuous Time vs. Discrete Time                                           | 47 |

|    |        | II.2.3 | Single Loop and Cascade Architectures                                                           | 49 |

8 Contents

| II.3    | $\Sigma\Delta$ ADC State-Of-The-Art                | 52  |

|---------|----------------------------------------------------|-----|

| II.4    | Conclusion                                         | 55  |

| TTTMC   | NBC System Level Specifications                    | 57  |

|         | <u>-</u>                                           |     |

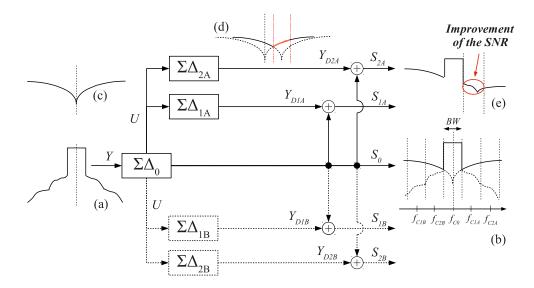

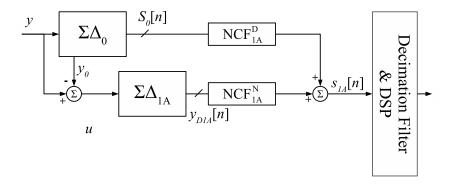

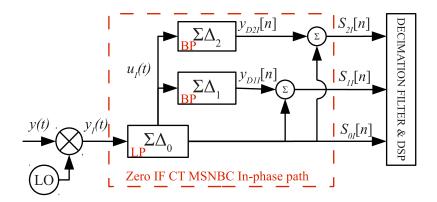

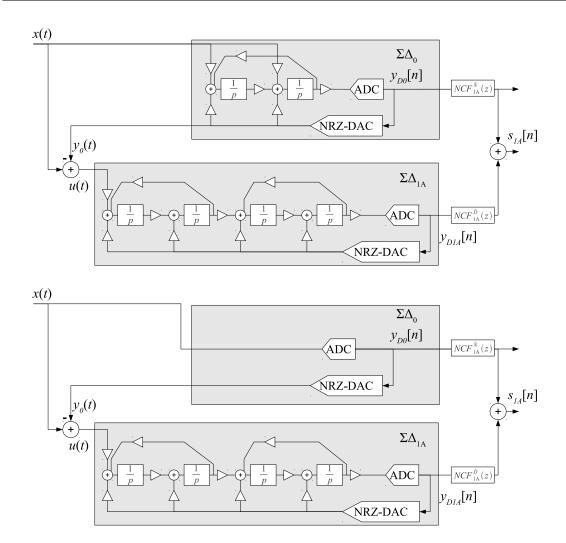

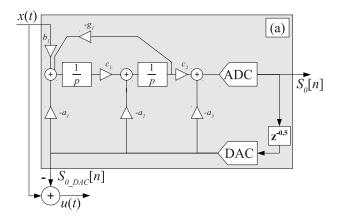

| 111.1   | The MSNBC Architecture                             |     |

|         | III.1.1 Mode of Operation                          |     |

|         | III.1.2 Degrees of Freedom / Key Design Parameters |     |

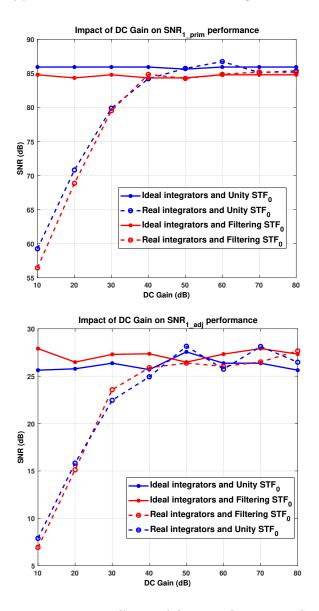

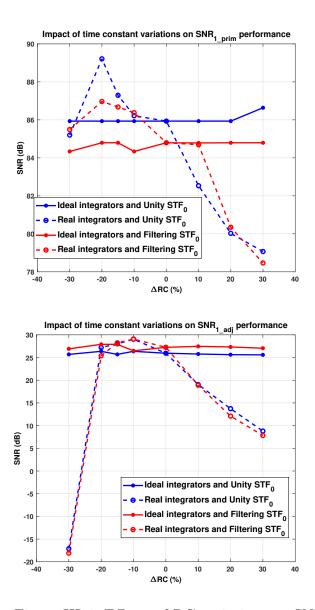

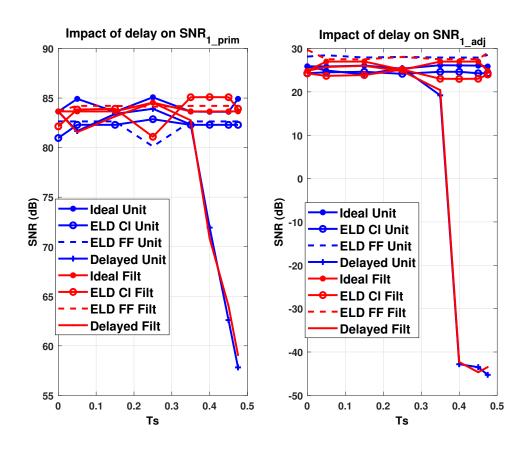

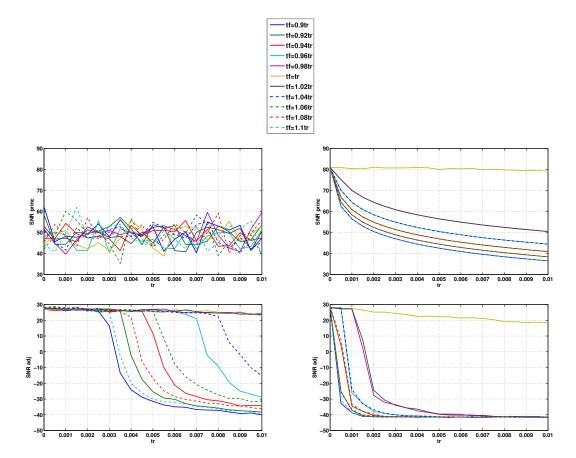

| III.2   | Impact of Non-Idealities                           | 61  |

|         | III.2.1 Loop Filter                                | 62  |

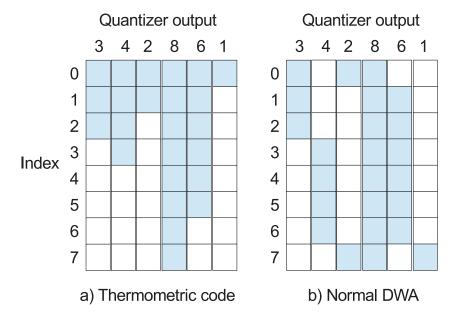

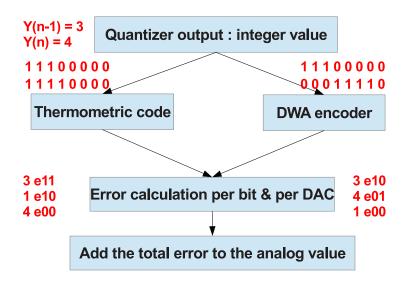

|         | III.2.2 Digital-to-Analog Converters               | 67  |

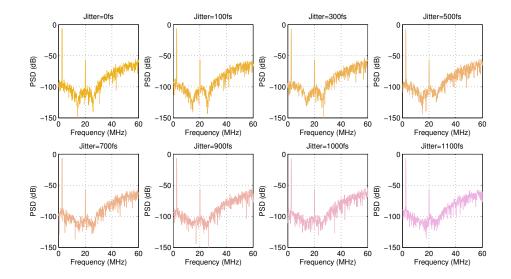

|         | III.2.3 The Clock Signal                           | 71  |

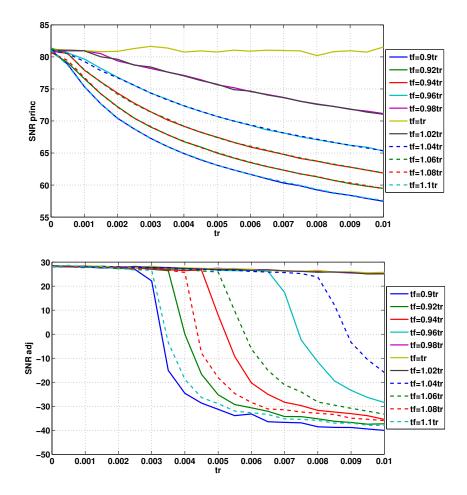

| III.3   | MSNBC Architectural Design Choice                  | 74  |

|         | III.3.1 Zero IF vs. Low IF                         | 74  |

|         | III.3.2 STF Choices                                | 80  |

|         | III.3.3 Signal Scaling                             | 83  |

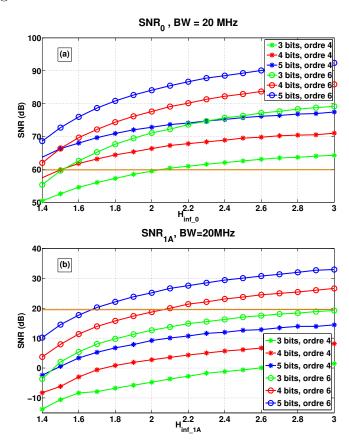

| III.4   | The MSNBC: Top level design                        | 84  |

|         | III.4.1 Design Parameters                          | 84  |

|         | III.4.2 2-4 MSNBC vs. 0-4 MSNBC                    | 85  |

| III.5   | Conclusion                                         |     |

| IV MS   | NBC Transistor Level Design And Measurements       | 89  |

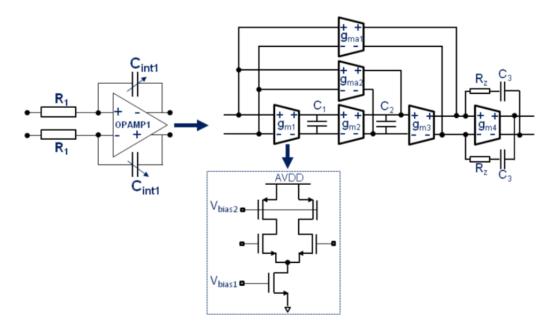

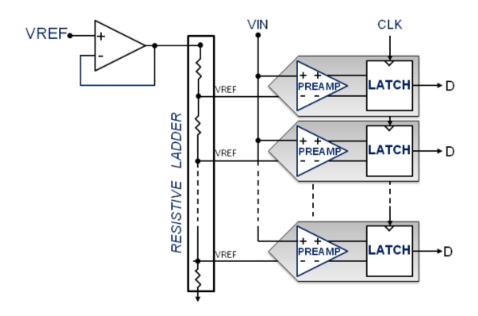

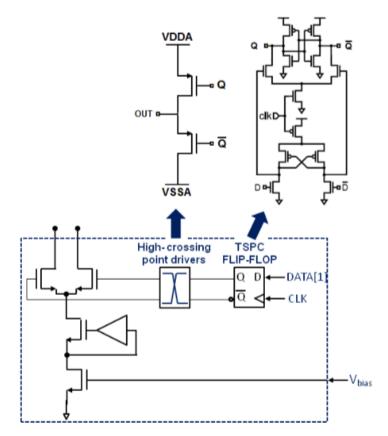

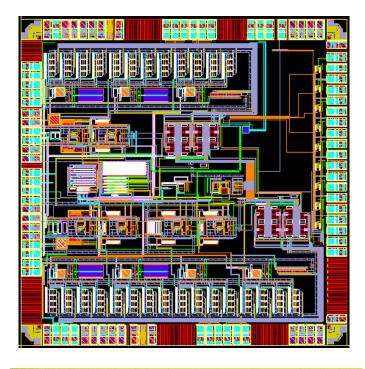

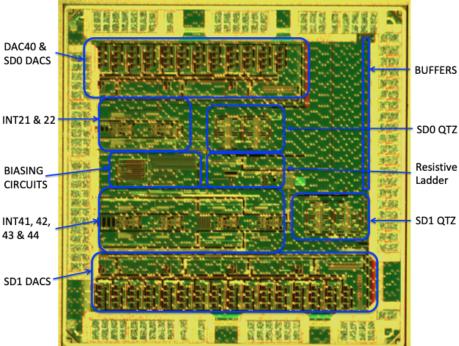

|         | Transistor Level Design                            | 89  |

|         | IV.1.1 Sub-blocks Design                           |     |

|         | IV.1.2 Simulation Results                          |     |

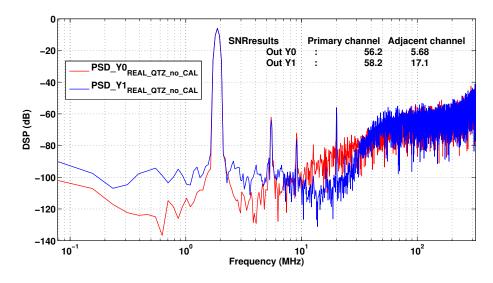

| IV 2    | MSNBC Measurements                                 |     |

| 1 V .2  | Wish De Weastrements                               | 100 |

| Conclu  | sion                                               | 107 |

| Publica | ations                                             | 109 |

10 List of Abbreviations

# List of Abbreviations

3GPP 3rd Generation Partnership Project

ACLR Adjacent Channel Leakage Power Ratio

ACPR Adjacent Channel Power Ratio

ADC Analog-to-Digital Converter

AM Amplitude Modulation

BP Band-Pass

BTS Base Transceiver Station

BW BandWidth

CDMA Code Division Multiple Access

CIFB Cascade-of-Integrators Feedback Form

CIFF Cascade-of-Integrators Feedforward Form

CMOS Complementary Metal Oxide Semiconductor

CT Continuous-Time

DAC Digital-to-Analog Converter

DE Drain Efficiency

DEM Dynamic Element Matching

DPD Digital Predistortion

DR Dynamic Range

DSP Digital Signal Processing

DT Discrete-Time

DWA Data Weight Averaging

EER Enveloppe Elimination and Restoration

ELD Excess Loop Delay

eMBB enhanced Mobile BroadBand

ENOB Effective Number Of Bits

ET Envelope Tracking

EVM Error Vector Magnitude

FBD Frequency Band Decomposition

FOM Figure Of Merit

GBW Gain BandWidth (product)

List of Abbreviations 11

IBN In-Band Noise

ICT Information and Communication Technology

IM InterModulationIoT Internet-of-Things

ISI Inter-Symbol Interferences

LIF Low Intermediate Frequency

LSB Least Significant Bit LTE Long Term Evolution

LUT Look-Up Table

MASH Multi-stAge Noise SHaping

MSNBC Multi-Stage Noise Band Cancellation

NCF Noise Cancellation Filter

NRZ Non-Return-to-Zero NTF Noise Transfer Function

OBO Output Back Off

OFDM Orthogonal Frequency-Division Multiple-Access

OOBG Out-Of-Band Gain OSR Oversampling Ratio

OTA Operational Transconductance Amplifier

PA Power Amplifier

PAE Power Added Efficiency

PAPR Peak-to-Average Power Ratio

PSD Power Spectral Density

PVT Process Voltage and Temperature

RF Radio Frequency

RSTF Residual Signal Transfer Function

RZ Return-to-Zero

SAR Successive-Approximation-Registers

SDR Signal to Distortion Ratio

SNDR Signal to Noise and Distortion Ratio

SNR Signal to Noise Ratio

SPI Serial-to-Parallel Interface

SQNR Signal to Quantization Noise Ratio

STF Signal Transfer Function

UMTS Universal Mobile Telecommunications System

WCDMA Wideband Code Division Multiple Access

ZIF Zero Intermediate Frequency

The world of Information and Communication Technology (ICT) is nowadays dominated by telecommunications, mobile Internet and many wireless applications.<sup>1</sup>

In order to understand the rise to prominence of telecommunications and mobile internet, it is useful to briefly review the evolution of the various network technologies. Starting with the late 1980s, the 2G network was first rolled out. Its key attributes included digital encryption of telephone conversations and the enabling of rapid wireless penetration rates. Essentially, the advent of the 2G network acted as a catalyst for the mobile data services such as text messages, i.e. SMS. In the ensuing two decades, the 2G was replaced by the 3G and then 4G telecommunication network. The key advantages of the new networks include fast information transfer rate and mobile broadband access to mobile phones to name but a few. The implications for the business world were far-reaching. For instance, telephone companies started offering services such as MMS, video calls and mobile TV technologies. Other businesses seize these advantages to introduce disruptive innovation. For instance, the ride-hailing mobile application Uber has taken advantage of the opportunities available thanks to the 4G network to really disrupt the taxi industry. In a similar vein, Netflix leveraged the improved speed of data transfer to introduce their offering, which changed the paradigm in the media industry.

As I embark on this thesis, there are growing talks of the 4G being replaced by the 5G network. The Fifth Generation (5G) mobile networks will see the initial deployment around 2020, promising wireless download speed of 10 Gbps for eMBB (enhanced Mobile Broadband) [2], and subsequently enabling billions of wireless connected devices for IoT (Internet-of-Things), autonomous driving, remote surgery. According to the World Economic Forum, the 5G holds the promise of sparking a profound digital transformation. Figure 1 [3] gives an overview of the different areas where the 5G technology can make a noticeable impact. For instance, its low latency potential will be very important for the industry on high-frequency/algorithmic

<sup>&</sup>lt;sup>1</sup>About 2-3% of the world-wide energy consumption is for ICT, which causes about 3% of the total CO2 emissions [1].

trading. Its reliability could transform the health care industry by enabling surgeons to remotely carry out complicated procedures on patients.

Figure 1: 5G mobile network applications

The usage cost of mobile services is likely to increase, and, in particular, the energy consumption might grow with the number of Base Transceivers Stations (BTS) and data centers in the network. Hence, as the demand for ICT services rises, higher and higher energy consumption is expected for mobile radio networks.

In order to preserve the environment, cellular network operators try to deploy various strategies to reduce energy consumption. BTS consume about 85% of the total energy of the network [4]. Their power consumption depending on the size, the coverage area and the technology used. The main axes of finding out efficient ways to reduce the energy consumed are: the optimization of hardware, the usage of renewable energy sources and the smart usage of resources through power saving models and efficient algorithms.

For hardware optimization, the power is consumed by the following components:

- The rectifier transforms the signal from AC to DC. The efficiency of the rectifier is about 92% for a conventional rectifier and about 97% for the case of latest products, for amperage loads between 40 90% [5].

- The Baseband Digital Signal Processing Circuit is considered as having a constant power consumption. This power is dissipated as heat and has to be removed, e.g., by the cooling system.

• The PA is a device that magnifies the amplitude of a signal. Radio-frequency (RF) PAs, such as the one used in cellular BTSs and broadcast transmitters, has an efficiency about 15%. The excess energy is transformed into heat.

- The feeder is the cabling system connecting the BTS to the antenna. In conventional BTSs, antennas and equipments are a few meters apart, and connected through a coaxial cable or Remote Radio Heads (RRH). Its efficiency approaches 1 when using RRH, and 0.5 when using coaxial cabling [4].

- The cooling system to keep the temperature of most components of the BTS within specified design limits. Air conditioners, free ventilation, forced-air cooling and heat exchangers are often the choice for radio sites. Such cooling requires as much power as one third of the heat power generated inside the BTS [6].

Given the efficiency of each of those components, a useful manner to optimize the hardware power consumption of a base station is to focus on the component with the lowest power efficiency, the PA.

In order to save energy and achieve high efficiency, PAs need to operate in the saturation region [7]. However, PAs exhibit high nonlinear distortion in that region, and this creates problems related to preserving high signal quality. The main trends in the design of wireless transmitters remains to provide enhanced transmitter functionalities with Digital Signal Processing (DSP) by using linearization techniques. There are a number of linearization techniques to improve the linearity of the power amplifiers and which enable, at the same time, to improve the efficiency. One of them, the digital predistortion (DPD), is of particular interest because it benefits from the technical advances of the digital part and communications systems increasingly use digital modulation.

Its implementation, in current and future emission chains, is a relatively low extra cost in the digital part, however it requires a measurement of the distortion generated by the amplifier and thus, a possibly dedicated, feedback path to convert the distorted analog RF signal to digital domain. In this system the analog-to-digital converter which is in charge of the measurement of the distorted signal must meet the requirements on the signal resolution and bandwidth. These needs are quite challenging in the context of digital predistortion and, in addition, here too, its energy consumption must be as minimum as possible.

Latest communication systems use relatively wide bandwidths. The distorted signal contains unwanted signals called intermodulation products, and is characterized by a spectrum P times wider than the original, where P is the considered

intermodulation order. In practice, we aim at digitizing at least intermodulation products of order 5. In addition, these signals are centered at a high transmission frequency. We realize that in this type of application, which is the digital predistortion, validating the sampling theorem establishes the frequency converter to very high values if we do not reduce the center frequency of the signal to a low value. Second, the resolution conversion of these distorted signals must be very high: because, on the one hand, multi-carrier signals have very high dynamics and on the other hand, the distortions may be small changes in the original signal. Various techniques are used to increase the performance of Analog-to-Digital Converters (ADC) as time-interleaving often used with pipelined ADCs or the parallelization of processing such as processing with decomposition into smaller frequency bands. Among the various converters,  $\Sigma\Delta$  modulators architectures are of particular interest: a high accuracy can be achieved for band-pass signals centered around high frequency with few components. Despite a strong limitation of the converter bandwidths due to their operating principle based on over-sampling, recent literature reports some circuits whose bandwidths allow to consider a possible use for broadband telecommunication applications. The purpose of this thesis is to develop and prove at silicon level an ADC for the measurement of the signal in the feedback path of DPD in base stations transceivers.

The remainder of the thesis proceeds as follows:

- Chapter 1 presents the architectures of PAs used in base station transceivers and their design constraints. It discusses several linearization techniques including digital predistortion. The proposed ADC specifications are then defined.

- Chapter 2 discusses the choice of the ADC type. It contains a discussion of the state-of-the-art  $\Sigma\Delta$  ADCs and key ADC design parameters are explained.

- Chapter 3 shows the high level design choices and degrees of freedom of our proposed ADC. The chapter elaborates on the choice of architecture and analyzes the impact of non-idealities of the selected architecture. This chapter concludes with high level simulations results.

- Chapter 4 explains the choices made for the transistor level design of the proposed ADC. It contains a discussion of the floor plan, transistor level simulations as well as measurements results of the ADC.

# Chapter I

# From DPD to ADC Specifications

In typical mobile communications BTS, the Power Amplifier consumes 50-80 % of the total power consumption [8]. With the increasing demand for higher data transfer rates in new communication standards, the situation gets worse. Therefore, the PA needs to be more power efficient.

# I.1 Power Amplifier

From that total DC power consumed, typically only approximately 30 % is converted into useful transmitted RF signals [9]. The main challenge in producing a high efficiency power amplifier in such applications is the high peak to average power ratio (PAPR) of the RF signal, which in some cases is in excess of 10 dB [8].

This is because the PA needs to be efficient not only at peak power but also at average power levels several dB's below where the PA would spend most of its time operating. As the demand for higher bandwidth increases, more complicated and dynamic modulation schemes are used, driving the signal PAPR increasingly higher. From a PA design standpoint, this puts a lot of pressure on the PA design community to provide solutions that continually improve PA efficiency and to react to the advancements in spectrally-efficient schemes, while respecting the stringent linearity requirements implicit in new wireless standards.

The 3G/4G wireless services not only have complicated modulations which reduce the Error Vector Magnitude (EVM) tolerance for systems, but also bring in nonconstant-amplitude waveforms. The PAPR for the amplitude of EDGE, WCDMA and CDMA2000 is 3.2-5 dB. [10] Furthermore, new spectrally efficient protocols employed in 4G communication systems utilize orthogonal frequency-division multiplexing (OFDM). These OFDM signals have even high PAPRs on their amplitude waveforms. The uplink PAPR of LTE is in the order of 7.5 dB [10] and >10 dB,

respectively.

|                 | GSM | EDGE | UMTS  | CDMA2000 | LTE   |

|-----------------|-----|------|-------|----------|-------|

| Max Power (dBm) | 35  | 29   | 26    | 25       | 25    |

| Min Power (dBm) | 7   | 7    | -48   | -48      | -40   |

| PAPR (dB)       | 0   | 3.4  | 3.4   | 3.5-5    | 6-8   |

| EVM limit       | -   | 9%   | 17.5% | -        | 12.5% |

| ACLR1 (dBc)     | 20  | 20   | 33    | 28       | 44.2  |

| ACLR2 (dBc)     | 60  | 60   | 43    | 43       | 44.2  |

Table I.1: Uplink Transmitters Requirements for PAs

Table I.1 contains some of the most relevant uplink transmitter performance parameters for 2G GSM, 3G WCDMA/CDMA 2000, and 4G LTE/WiMAX. A saturated or switching PA can deliver a maximum output power of 35 dBm and an efficiency of >60 % at this power level for GSM (an industry benchmark). The main impact of EDGE is to introduce an amplitude component to the modulation scheme (8PSK). Maximum output power is reduced to 29 dBm, partly in recognition of the crest factor of 3.2 dB and partly due to the need to use a linear amplifier with reduced efficiency. Power control range is still a modest 22 dB. The industry-driven target figure for PAs used for EDGE signals is 45 %. As far as WCDMA and CDMA2000 are concerned, the challenge for efficiency recovery is similar to EDGE despite the apparent threat from an increased power-control in the range of 75 dB. Fortunately, power budgets in the transmitter are such that worthwhile efficiency enhancement only applies to the top 20 dB dynamic range.

Unlike constant-amplitude modulations such as GSM, the non-constant-amplitude modulated signals with the inherent high PAPR and wide bandwidth require highly linear PAs having very low signal distortion. One way for the PA to satisfy the stringent linearity requirements is to back off from its compression region. This is a major bottleneck for realizing highly efficient mobile transmitters.

#### I.1.1 State-of-the-Art of PAs Used in BTS

The efficiency of a PA, or drain efficiency (DE), is defined as the ratio of the fundamental output power to the DC supplied power. Another metric that is often used is power added efficiency (PAE) which takes into account the gain of the PA, and is defined as the ratio of the difference between output and input fundamental power over the DC supplied power. For a PA with high gain, DE and PAE will be similar, but if the PA gain goes below for example 10 dB, the DE and PAE difference would

be more than 10% [11].

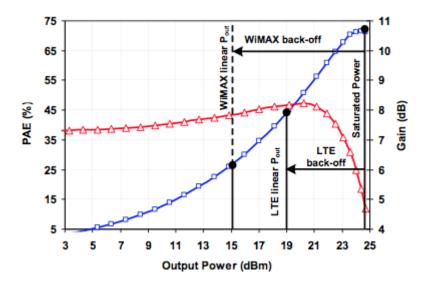

Figure I.1: Power Added Efficiency of a PA

Figure I.1 shows the efficiency of a typical 1-stage common-emitter SiGe PA. The PAE reaches the peak value at saturation power, but drops dramatically at back-off that depends on different PAPR values and different linearity specifications. This is opposed to saturated PAs that work with constant-amplitude signals but exhibit high efficiency.

Several techniques have been developed in improving PA efficiency. The basis of these techniques is the reduction of the overlapping region between the current and the voltage at the device current generator plane by reducing the conduction angle, as well as increasing the drive level to an optimum point [12].

While high-efficiency PA modes yield promising efficiency gains, they are only efficient near peak power when the device starts to go into compression. However, when the PA operates below peak power under output back-off (OBO) conditions, the efficiency drops significantly. Signals with high PAPR such as LTE and WCDMA present a challenge to a PA in maintaining efficient operation over dynamic range, as the PA spends most of its time in output back-off.

Therefore, in this backed-off region of operation, a different solution is needed to maintain the same efficiency performance achieved at peak power. The 5G waveforms with high PAPR will degrade PA's efficiency at power back-off, making both Doherty PA and supply-modulated PA (envelope tracking (ET), envelope elimination and restoration (EER)) very attractive for efficiency enhancement of 5G PA design.

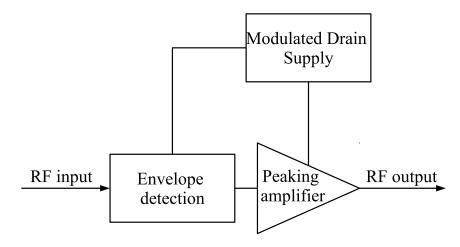

#### **Envelope Tracking PA**

The envelope tracking technique modulates a device's DC supply according to the input envelope magnitude to improve the efficiency during output back-off. The approach evolved from the EER amplifier technique of Kahn [13]. In ET, an envelope amplifier is used to bias the drain of the RF PA based on the input envelope signal as shown in Figure I.2. The envelope information is obtained either through an envelope detector on the input path or digitally from baseband processing. Its relationship with the drain bias voltage is defined by an envelope shaping function to generate the desired ET system-level efficiency shown in Figure I.2. The overall efficiency of an ET PA is calculated as the product of the efficiency of the RF PA and the envelope amplifier. Therefore to improve the ET PA efficiency, careful design considerations must be given to both amplifiers.

Figure I.2: Enveloppe Tracking PA

One constraint to implement ET in macro base stations is the lack of efficient, linear and sufficiently wide-band high-power supply modulators [14]. This limitation is mainly due to the trade-off between the transistor breakdown voltage and its switching speed, hence ET implementations tend to be limited to low power applications such as mobile phones [15]. A simplified version of ET called the average power tracking (APT) is widely used for mobile phones PA's where the supply voltage is changed slowly. However with the advancement of low-power modulators, a complete ET system is emerging as the future trend, especially with ET's ability to work over extended bandwidths and accommodate multi-band operation [16]. The other issue with the ET supply modulator is that it can potentially be a source of distortion for the RF PA. It therefore makes sense that much of the ET research focus is around the ET supply modulator, for example in [17],[18].

Recent works in this field have further improved efficiency numbers or higher frequency of operation. A GaN HEMT operating in class-E is used in [19] in an ET system at 2.6 GHz. With the RF PA having a drain efficiency of 74% and the ET modulator at 92% efficiency, the overall ET efficiency was 60% when a 6.5 dB PAPR 10 MHz LTE signal was applied producing a 40 W average output power. In [20] an ET PA utilizing a GaN device operating in inverse class-F at 880 MHz was able to produce a PAE of 53% at 7.4 W output power for a 6.6 dB PAPR 20 MHz LTE signal. A higher bandwidth was achieved in [21] where an X-band GaN MMIC PA was used in ET for a 60 MHz LTE signal with 6.6 dB PAPR. With the RF PA operating in class-E at 9.23 GHz, the overall PAE achieved was 35% at 1.1 W average output power.

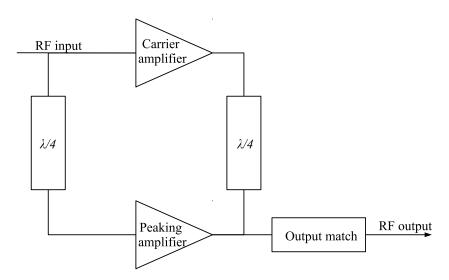

#### Doherty PA

The Doherty architecture was first introduced by William H. Doherty in 1936 to improve the PA efficiency in amplitude modulation (AM) broadcasting applications [22]. The basic form of a Doherty PA consists of a carrier amplifier, typically biased in class-AB, and a peaking amplifier biased in class-C as shown in Figure I.3. This classical structure can maintain high-efficiency operation over 6 dB OBO using the concept of load modulation [23].

Figure I.3: Doherty PA

The high-efficiency output range can theoretically be extended further up to 12 dB OBO using a 3-way [24] or even 18 dB for a 4-way Doherty [23]. An asymmetric Doherty amplifier, where the peaking device is larger than the carrier device is also used to extend the high-efficiency region as for example up to 12 dB OBO as

demonstrated in [25], with only a 7%-point drop over the dynamic range. The application of an "envelope tracking" technique on the gate bias of the peaking device was presented in [26] to address load modulation issues that are causing the dip in the high efficiency region. The work in [27] tackles this by applying ET on the drain bias of the peaking device, and a relatively flat high efficiency performance was achieved over 18 dB of dynamic range in a simulation environment. However the analysis did not include a fabricated hardware and the efficiency of the drain supply modulator was not considered.

The main limitation of Doherty PA is the narrow bandwidth introduced by the use of the quarter wavelength combining transformer. This presents a challenge in 4G LTE where not only the bandwidth is wider, but with carrier aggregation, PA's ideally need to accommodate multiple-bands. Research focusing on extending the bandwidth of a Doherty PA is ongoing and recent examples include [28] which is capable of handling a 100 MHz instantaneous bandwidth, and [29] where a 1.5 - 2.14 GHz design was developed corresponding to a 35 % fractional bandwidth.

In [30], a multiband Doherty was designed and fabricated for 1.9, 2.14, and 2.16 GHz obtaining a 60 % PAE at 6 dB OBO. In a more recent study, a quadband Doherty PA was developed at 0.96, 1.5, 2.14, and 2.16 GHz, although with a relatively lower PAE at 6 dB OBO, ranging from 20 to 43 % [31]. There are also patented wideband and multiband Doherty PA's as shown in [32].

Doherty is currently the architecture of choice for base station power amplifiers [23], mainly because of its relative simplicity in comparison with other highly efficient solutions such as ET.

# I.1.2 Linearization Techniques

The design of the power amplification stage is driven by a linearity and power efficiency tradeoff. Doherty and ET power amplifiers have a high efficiency and operate in compression or even saturation. Consequently, it produces signal distortions. Thus, the need for some form of linearization is essential.

"Linearization" is a process which enables linear amplification of a signal in the presence of nonlinear components, by canceling the distortion introduced by those components. There are 3 main techniques to improve linearity of power amplifiers: feedback, feed forward and predistortion.

Table I.2 compares those techniques in terms of size, bandwidth, efficiency and harmonic distortion cancellation. Depending on the application and the requirement of a system, one technique is preferred to another.

The feedback technique has moderate linearity results and is simple to imple-

| Technique     | Cancellation | Bandwidth   | Efficiency | Size   |

|---------------|--------------|-------------|------------|--------|

| Feedback      | Low          | Low         | Medium     | Medium |

| Feedforward   | High         | High        | Low        | Large  |

| Predistortion | Medium       | High/Medium | High       | Small  |

Table I.2: Comparison of PAs linearization techniques

ment. Moreover, this technique decreases the gain of the system, and there are some stability issues to deal with. Its narrow band of operation, makes it not suitable for 4G/5G mobile standard.

The concept of feedforward systems is simple, but its hardware implementation is quite costly.

Feedforward methods exhibit a good linearization performance with a high stability and wideband signal capability. The feedforward technique is historically less popular and is mostly applied in base stations. However, it has low efficiency and high complexity resulting in the big size of the circuit and high cost.

For example, feedforward is mainly used in base station transceivers instead of PA handsets because of its high cost. However, with all the progress made in the digital field and the need to integrate and miniaturize systems, DPD is used in many applications nowadays.

State-of-the-art power amplification systems often use a Doherty PA for high efficiency at output power backoff, and a digital predistorter to restore the required linearity performance. Digital predistortion is currently the preferred linearization technique and is widely used for applications with, typically, up to 20 MHz bandwidth. [33]

# I.2 Digital Predistortion Technique

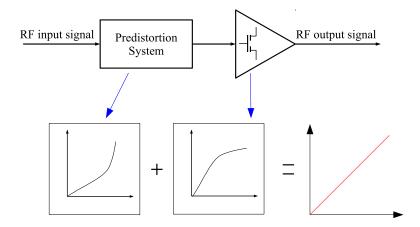

Predistortion is the most popular linearization technique of power amplifiers today. This technique consists in applying the inverse characteristics of a PA to the input signal before feeding it to the PA, so that the cascade behaves as a linear amplification system, as presented in Figure I.4. Thus, this inverse function called Predistorter compensates for AMAM and AMPM distortions.

# I.2.1 DPD Implementation

The predistortion function can be implemented with analog components, or DSP operations and digital components. Then we talk about Analog and Digital pre-

Figure I.4: Predistortion principle

distortion. Analog predistortion uses components like diodes and FET for implementing the predistorter. The cubic analog predistortion technique mainly uses non linear components, and RC circuit for phase shift which aims to eliminate 3<sup>rd</sup> and 5<sup>th</sup> order distortion. The diode/FET analog predistortion uses a parallel diode or a FET transistor for implementing the inverted magnitude and phase of the PA transfer function.

Analog predistortion is not adapted to cancel high order effects due to signal expansion and compression which are more difficult to handle in analog domain compared to digital. Moreover, analog predistortion is not well suited to system with high memory effects because this requires the implementation of a high number of analog delays. The main advantages of the analog predistortion are simplicity of realization, low cost, simple integration procedure, and possibility to linearize wideband power amplifiers. However this technique has small-to-moderate linearizing performance, power loss in the additional RF components which decreases the overall efficiency, and difficulty in providing adaptation, which significantly increases complexity of the circuit.

With the progress of DSP and FPGA, processors can nowadays do more complex operations with very good accuracy at a very low price. Digital predistortion has thereby become a great linearization technique research area for the last years as DSP are used to estimate the PA model and calculate the predistortion function. DSP increases the possible number of algorithms that can be used to estimate PA characteristics. Combined with feedforward or feedback, DPD benefits from high flexibility, controllability and possibilities to provide algorithm.

Depending on where the predistortion is applied, predistortion can be implemented in RF, IF or baseband. When the predistorter is applied before the up-

conversion, we talk about baseband predistortion. When the signal is up-converted before being predistorted, it is an RF predistorter and when it is between two upconversion, it is called intermediate frequency (IF) predistortion.

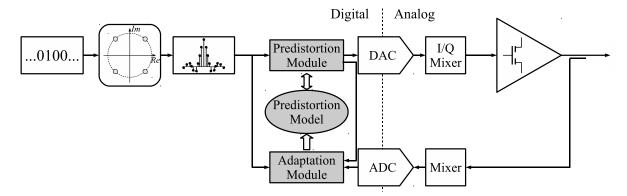

Figure I.5: Main components of a DPD system

A simplified DPD architecture in Figure I.5 allows us to identify conceptually the main subsystem components of a DPD system:

- Components in the transmission and acquisition paths: mixers and the PA.

- Data Converters: the ADC and DAC.

- DSP and control system: digital hardware for the predistorter.

Each of the subsystems contributes to the design targets which are evaluated in terms of linearity, dynamic range, bandwidth, power consumption and hardware cost. However, new communications bandwidths lead to high design constraints on the ADC.

# I.2.2 ADC Implementation Trade-offs

Although it already seems to be a well-established technique at the current stage, DPD is still facing new challenges. New issues are coming with recent modulation schemes and multi-band scenarios presenting higher PAPR leading to higher order of non-linearity for the PA. This trend has a large impact on DPD design in many aspects, not the least of which is the wide band signal to be processed [34]. DSPs and Data converters are highly impacted by this evolution because the number of coefficients required to model the PA inverse transfer characteristic increases and at least 5 or 7 times the original signal bandwidth have to be processed which is a huge band. Generally, the DPD system contains ADCs to sample the PA output and feed it back to the DPD, in which the transmission path and acquisition path are both based on direct conversion structure.

One issue relating to ADC in the acquisition path is the resolution. Before training the DPD model, the output signal of the PA is digitized. The number of quantization bits depends on the actual system requirement. In order to have a noise floor at  $-80\,\mathrm{dBc}$ , a 14-bit ADC is needed. Designing a 14-bit ADC is challenging and costly [35] for the considered bandwidth (hundreds of MHz). It is therefore desirable to reduce the resolution; however, this is not a straightforward task, since reducing the resolution of ADC is equivalent to increasing the noise floor of the feedback signal, which is critical to the accuracy of DPD modeling. Liu et al. [36] proposed a method to reduce the ADC dynamic range, but a minimum 8-bit ADC is required to achieve linearization performance comparable to the conventional DPD.

Besides the resolution, the main issue relating to ADC in DPD implementation is the bandwidth requirement of the feedback path that is used to capture the output signal from the PA for the purpose of model extraction. In DPD, the bandwidth of the feedback path usually requires five times the signal bandwidth. For an acquisition path that is based on direct conversion structure, for instance, the sampling rate of the ADCs should be at least 500 MHz if an LTE-Advanced signal is applied. The existing and forthcoming data converter technologies could hardly meet this requirement.

Some solutions have been proposed to reduce the signal bandwidth requirement. The band-limited method was proposed in [37], but requires an extra bandpass filter in the RF transmit chain that is difficult and costly to design. The analog aliased sampling method in [38] can reduce the sampling rate, but it needs additional analog aliasing operation. The spectral-extrapolation-based algorithm was reported in [34], and a forward model was first carried out and then DPD coefficients can be estimated. In [39], a two-stage DPD, i.e., a static nonlinear box cascaded with a dynamic weak nonlinear box, was proposed to decrease the feedback bandwidth. All the methods mentioned above require the acquisition bandwidth not narrower than the signal bandwidth.

There have been substantial research efforts over the past 20 years with respect to developing efficient and elaborate DPD techniques for various single-band transmission schemes where linearization for the whole transmit band is essentially pursued. These conventional DPD approaches take as their inputs the full composite transmit band, and we thus refer to these DPD approaches as full-band DPD.

# I.3 ADC Specifications for DPD

The feedback path of a DPD system can be considered as a direct conversion receiver (DCR). DCRs suffer from RF and baseband impairments such as I/Q imbalance and nonlinear distortions [40]. In order to set the design parameters for the ADC in the full-band DPD feedback path, we will successively consider different nonlinear effects and evaluate their impact on DPD correction.

For this study, the correction performance are simulated using a 20 MHz mono-carrier LTE signal. This signal is distorted using the memory polynomial PA model proposed in [41]. The linearization of this system is achieved with a memory polynomial model identified by a least-square method [41]. The nonlinear order of the inverse model is set to 9 and its memory depth is 3 in order to provide 55 dB adjacent channel power ratio and 0.2% error vector magnitude when all blocks in the feedback path are ideally linear and there is no quantization error. This configuration exhibits some margins compared to the standard specifications.

#### I.3.1 Mixer I/Q Imbalance

As a first step, we focus on the effect of the I/Q imbalance. I/Q imbalance is assumed to be caused by the mixer and the baseband I/Q paths. We assume in this subsection that the mixer I/Q imbalance predominates over the baseband I/Q imbalance and there is no quantization error. As explained in [40], the I/Q imbalance can be modeled on the complex baseband signal with the following equation:

$$\tilde{y}(t) = \frac{1 + g_m e^{-j\Phi_m}}{2} y_{att}(t) + \frac{1 - g_m e^{j\Phi_m}}{2} y_{att}^*(t), \tag{I.1}$$

where  $\tilde{y}(t)$  and  $y_{att}(t)$  are respectively the I/Q imbalanced and the ideal baseband complex envelope,  $g_m$  is the relative amplitude mismatch between I and Q branches,  $\Phi_m$  is the phase mismatch and  $(\cdot)^*$  denotes the complex conjugate.

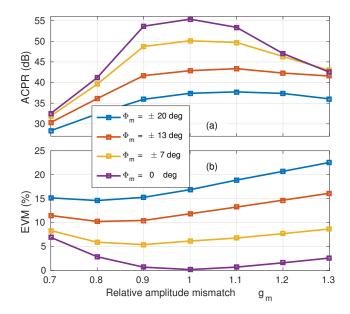

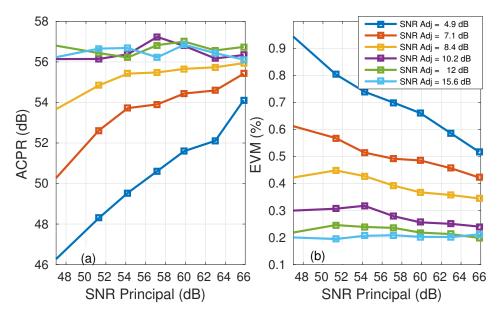

The upper and lower parts of Figure I.6 show respectively the ACPR and the EVM versus the relative amplitude mismatch  $g_m$ . In both graph, each line corresponds to a given phase error  $\Phi_m$  ( $\pm 20^{\circ}$ ,  $\pm 13^{\circ}$ ,  $\cdots$ ,  $0^{\circ}$ ). As expected, the worst results are achieved for large values of phase error and large relative amplitude mismatch. It can be seen on Figure I.6 (a) that the relative amplitude mismatch must be such that  $0.9 \leq g_m \leq 1.1$  and the phase error should be less than about  $10^{\circ}$  to meet the 3GPP LTE standard requirements [42]. Regarding the EVM (Figure I.6 (b)), the standard requirements are met for the same range of  $g_m$  and  $\Phi_m$  as ACPR.

Figure I.6: DPD performance in terms of ACPR (a) and EVM (b) vs I/Q mismatch: simulation results

#### I.3.2 Fullband Nonlinear Feedback Path

The effect of a nonlinear distortion generated in the feedback path is now considered. This distortion may be caused by compression in the active blocks of the feedback path. We assume that distortions are modeled by a 3<sup>rd</sup> order nonlinearity and that higher orders nonlinearities have minor effects. As mentioned in [40], this nonlinearity can be modeled on the complex baseband signal by:

$$\tilde{y}_{BB}(t) = y_{att}(t) + \alpha \left( [y_{att}^*(t)]^2 + 3 y_{att}^2(t) \right) y_{att}^*(t), \tag{I.2}$$

where  $\alpha$  is the nonlinearity coefficient. We define the fullband signal to distortion ratio (SDR) as:

$$SDR = \frac{P_{mean} \{y_{att}(t)\}}{P_{mean} \{\alpha ([y_{att}^{*}(t)]^{2} + 3 y_{att}^{2}(t)) y_{att}^{*}(t)\}},$$

(I.3)

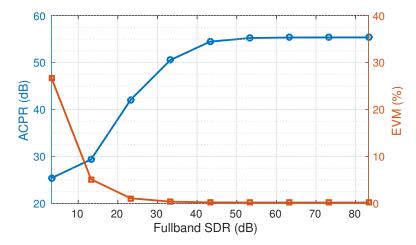

Figure I.7 shows the ACPR and EVM of the linearized PA output obtained by simulation. As long as the distortions generated by the feedback path are low enough  $(SDR \geq 55\,\mathrm{dB})$ , correction performance are maximum. For  $SDR \leq 55\,\mathrm{dB}$ , the ACPR drops. The EVM is less sensitive to this  $3^{\mathrm{rd}}$  order nonlinearity as it remains constant for a wider range of distortion level: its effect is significant for  $SDR \leq 40\,\mathrm{dB}$ . In order to cope with circuit non idealities, the target linearity of the ADC is set to  $60\,\mathrm{dB}$ .

Figure I.7: DPD performance in terms of ACPR and EVM vs nonlinearity of the feedback path

### I.3.3 Subband ADC Requirements

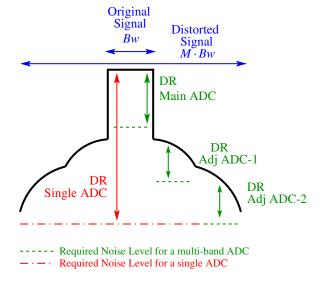

The non-linearity study presented above assumed that a full-band single ADC is used to digitize the signal in the feedback path of the DPD. This ADC needs to have a high dynamic range in  $M \times BW$  bandwidth in order to capture both high power signals and low power distortion signals (IMD products).

Subband DPD [43] is particularly attractive as it relaxes the design of the ADC. With the subband approach, as presented in Figure I.8, the main signal band and adjacent bands will have different DR requirements.

Figure I.8: Single ADC vs. multi-band ADC

The digitization is performed with several ADCs, one for the main signal and

one for each subband. This architecture provides new degrees of freedom such as the possibility of having different quantization noise level for each subband. The ADC dimensioning is now studied assuming a multi-band ADC.

Figure I.9: DPD performance in terms of ACPR and EVM vs. subband quantization SNR; ACPR without DPD:  $30\,\mathrm{dB}$ ; EVM without DPD:  $4.3\,\%$

The difference in DR requirements can be achieved by setting different quantization step sizes for the modulator quantizer in each subband. The effect of this subband quantization on the linearization results is simulated and ACPR and EVM are shown in Figure I.9. The x-axis is the SNR in the principal subband, which corresponds to the ideal 20 MHz transmit band and each colored line represents a specific SNR in the 20 MHz adjacent subband.

As expected, the higher the SNR, the better the ACPR and EVM. The ACPR is independent of principal subband SNRs between 48 and 66 dB for adjacent subband SNR greater than 10.2 dB. The EVM has a similar characteristic for adjacent subband SNRs greater than 12 dB.

By considering the input signal peak-to-average power ratio in these simulation results, the minimum performance of a multi-band ADC is set to  $60\,\mathrm{dB}$  SNR in the principal subband and  $22\,\mathrm{dB}$  SNR in the adjacent subband.  $^1$

<sup>&</sup>lt;sup>1</sup>The SNR in the adjacent subband may seem low. However the power of the signal in this subband is very low. For sake of clarity, the detailed spectrum decomposition is not discussed here.

I.4. Conclusion 31

### I.4 Conclusion

In this chapter, we saw several techniques to solve the linearity and efficiency tradeoff of RF power amplifiers in base station transceivers. DPD is an attractive linearization technique which is nowadays extensively used. Non-linearities in the

feedback path of DPD alter the signal used for the PA inverse model computation.

Simulations show that for some distorsion levels, DPD is not significantly affected

and for high distorsion levels, DPD performance are reduced because the extracted

PD model is erroneous. In case of a full-band DPD for LTE applications, the feedback ADC should at least have  $60 \, \mathrm{dB}$  SNR in  $M \times BW$  with M is the highest

significant nonlinear order at the output of the PA and BW the input signal bandwidth. For a sub-band DPD approach the main sub-band ADC should at least have  $60 \, \mathrm{dB}$  SNR and adjacent sub-bands should have  $22 \, \mathrm{dB}$  SNR.

With these requirements, several ADC architectures can be used to digitize the attenuated output of the PA in a DPD system.

# Chapter II

# Analog-to-Digital Converters State-Of-The-Art

An Analog-to-Digital Converter transforms real world signals like temperature, voltage, light intensity into a digital signal. This digital signal can thus be easily computed, processed or stored. In DPD for example, digital signals are required to estimate the Power Amplifier model and apply predistortion algorithms. Thus, the accuracy of the analog-to-digital converter is crucial as it affects the PA model calculation.

# II.1 A/D Conversion

Analog signals are converted in the digital domain with two functions: sampling and quantization.

# II.1.1 Sampling and Quantization

Analog signals are continuous both in time and amplitude and their spectrum contains non-zero tones in a finite frequency band as an effect of their continuity in amplitude. The analog-to-digital conversion requires the analog input signal to firstly be sampled by a sample-and-hold which transforms it into an analog, discrete-time signal, only changing its amplitude at periodic intervals. Because sampling introduces instantaneous amplitude changes in the analog signal, the spectrum of the sampled signal has infinite bandwidth, by replicating the input signal spectrum around the multiples of the sampling frequency. A bandwidth constraint on the analog input should then be taken into account.

According to the Nyquist Theorem, to prevent information loss, a signal must

be sampled at a minimum rate of  $f_N = 2$  BW, often referred to as the Nyquist frequency. Sampling with frequencies lower than  $f_N$  introduces aliasing which changes the image of input signal spectrum in the sampled signal. Aliasing defines the overlapping of the input signal spectrum with the first replica of itself introduced by sampling at  $2 \cdot f_N$ . On the basis of this criterion, ADCs in which analog input signal is sampled at the minimum rate  $(f_s = f_N)$  are called Nyquist rate ADCs. Conversely, ADCs in which  $f_s > f_N$  are called oversampling ADCs. How much faster than required the input signal is sampled is expressed in terms of the oversampling ratio (OSR), defined as

$$OSR = \frac{f_s}{2 \cdot BW} \tag{II.1}$$

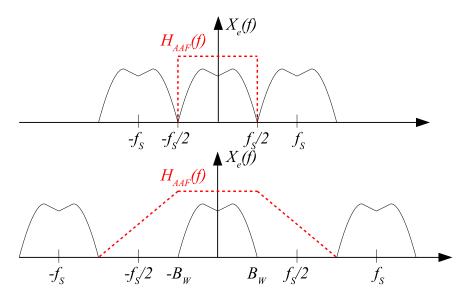

The oversampling process influences the anti-aliasing filter (AAF) requirements of the ADC as showed in Figure II.1. In Nyquist-rate ADCs, the input signal bandwidth BW coincides with  $f_s/2$ , aliasing will occur if the input signal contains frequency components above  $f_s/2$ . High-order analog AAFs are thus required to implement sharp transition bands capable of removing out-of-band components with no attenuation of the signal band.

Figure II.1: AAF requirements

Given that  $f_s/2 > BW$  in oversampling ADCs, the replicas of the input signal spectrum that are created by the sampling process are farther apart than in Nyquistrate ADCs. Thus, frequency components of the input signal in the range  $[BW, f_s - BW]$  do not alias within the signal band, so that the filter transition band can be smoother. This greatly reduces the order required for the AAF and simplifies its design.

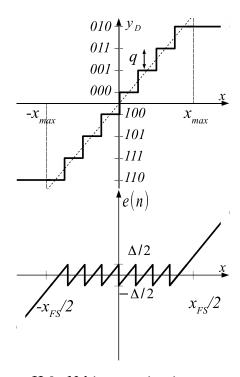

The quantization operation consists in sampling the signal in the amplitude domain as presented in Figure II.2. Input amplitudes within the full-scale (FS) input range  $[-X_{FS}/2, +X_{FS}/2]$  are rounded to 1 out of the 2N (where N is the resolution of the quantizer) different output levels, which are usually encoded into a binary digital representation.

Figure II.2: N-bit quantization operation

If these levels are equally spaced, the quantizer is said to be uniform and the separation between adjacent output levels is defined as the quantization step

$$\Delta = \frac{Y_{FS}}{2N - 1} \tag{II.2}$$

where  $Y_{FS}$  stands for the full-scale output range. The quantizer operation thus inherently generates a rounding error that is a nonlinear function of the input. If q(n) is kept within the range  $[-X_{FS}/2, +X_{FS}/2]$ , the quantization error e(n) is bounded within  $[-\Delta/2, +\Delta/2]$ . Assuming q(n) changes randomly from sample to sample within the range  $[-\Delta/2, +\Delta/2]$ , e(n) will also be uncorrelated from sample to sample. Under these requirements, the quantization error can be viewed as a random process with a uniform probability distribution in the range  $[-\Delta/2, +\Delta/2]$ . The power emerging from the quantization error can thus be computed as

$$\bar{e^2} = \sigma_e^2 = \int_{+\infty}^{-\infty} e^2 PDF(e) de = \frac{1}{\Delta} \int_{+fs/2}^{-fs/2} e^2 de = \frac{\Delta^2}{12}$$

(II.3)

The former assumption implies that, the power of the quantization error will also be uniformly distributed in the range [-fs/2, +fs/2], yielding to:

$$\bar{e^2} = \int_{+\infty}^{-\infty} S_E(f) df = S_E \int_{+fs/2}^{-fs/2} df = \frac{\Delta^2}{12}$$

(II.4)

Therefore, the power spectral density (PSD) of the quantization error in the range [-fs/2; +fs/2]

$$S_E = \frac{\Delta^2}{12fs} \tag{II.5}$$

On the basis of this approximation of the quantization error to a white noise, the performance of ideal ADCs can be easily evaluated.

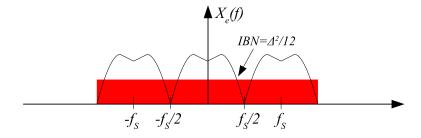

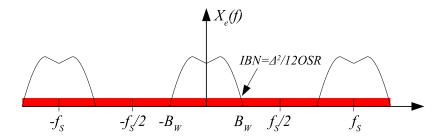

Figure II.3: Quantization noise in Nyquist and oversampled ADCs

For a Nyquist ADC, all the quantization noise power falls inside the signal band and passes to the ADC output as part of the input signal itself as illustrated in Figure II.3. Conversely, if an oversampled signal is quantized, because  $f_s > 2BW$ , only a fraction of the total quantization noise power lies within the signal band. The inband noise power (IBN) caused by the quantization process in an ideal oversampling ADC is thus,

$$IBN = \int_{+BW}^{-BW} SE(f)df = \int_{+fs/2}^{-fs/2} \frac{\Delta^2}{12fs} df = \frac{\Delta^2}{12OSR}$$

(II.6)

so that the larger the OSR, the smaller the IBN.

Data converters are all evaluated by some performance metrics which allows to compare them and helps to select the appropriate converter for a given specification.

#### II.1.2 Performance Metrics

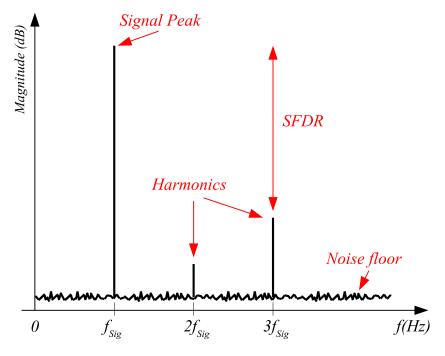

Most Analog-to-Digital Converters performance metrics are obtained by translating the output signal of the ADC in the frequency domain. The most commonly used dynamic performance are expressed with Signal-to-Noise Ratio (SNR), Total Harmonic Distortion (THD), Signal-to-Noise plus Distortion Ratio (SNDR), Dynamic Range (DR), Spurious Free Dynamic Range (SFDR).

Those metrics are illustrated in a signal spectrum in Figure II.4, where exemplarily a flat noise floor with a one tone signal and its harmonics are illustrated.

Figure II.4: SNR

- The signal-to-noise ratio of a converter is the ratio of the signal power to the noise power at the output of the converter, specified for a certain input amplitude and bandwidth.

- The signal-to-noise and distortion ratio is the ratio of the signal power to the noise and all distortion power components. Thus, the corresponding spectra are obtained by applying a signal at  $f_{sig} \leq f_B/3$  to include at least the second and third harmonic inside the band of interest.

- The dynamic range is the ratio between the maximum signal power and minimum detectable signal power within a specified bandwidth. It is the root mean squared value of the maximum amplitude input sinusoidal signal.

- The spurious free dynamic range is defined as the ratio of the signal power to the power of the strongest spectral tone. Its importance strongly depends on the application, since it dominates the resulting ADC linearity.

- Total harmonic distortion is the ratio of the sum of the signal power of all harmonic frequencies above the fundamental frequency to the power of the fundamental frequency. The  $x^{\text{th}}$  harmonic itself is the ratio between the signal power and the power of the distortion component at the  $x^{\text{th}}$  harmonic of the signal frequency.

It should be noted that these performance parameters are all relative numbers. Information about the (maximum) input power is needed for a complete qualification.

Because one parameter is sometimes not enough to compare ADCs, Figure Of Merits (FOM) combine several ADC parameters such as speed, bandwidth, conversion resolution, power consumption to compare ADCs. Two FOMs are widely used in ADC literature.

The Walden FOM [44] illustrates the power efficiency of an ADC with the following expression:

$$FOM_W = \frac{P}{2BW \times 2^{ENOB}},\tag{II.7}$$

where P is the power consumption of the ADC, BW denotes the ADC's bandwidth and ENOB its Effective Number Of Bits. The Walden FOM is expressed in picojoules per conversion-step (pJ/conv). In addition to the Walden Figure of Merit, ADCs can also be compared using the Shreier FOM [45].

$$FOM_S = SNDR(dB) + 10\log_{10}(\frac{BW}{P})$$

(II.8)

If  $FOM_S$  is rewritten in linear form and inverted, it is then proportional to

$$\frac{P}{BW \times 2^{2 \times ENOB}} \tag{II.9}$$

Equations (II.8) and (II.9) account for the fact that due to thermal noise limitations, achieving twice the conversion accuracy requires 4 times increase of the

power consumption. Shreier FOM is still standard in literature and is better to use to compare ADCs with same resolution.

#### II.1.3 ADC Architectures

Analog-to-Digital Converters cover many applications depending on the requirements of the system regarding speed or power consumption. Depending on the targeted application, different ADC architectures such as Flash ADC, Sigma Delta ADC, Pipeline ADC, SAR ADC for example can be used.

The flash topology is the typical choice for high-speed, low-resolution converters. Flash ADCs achieve the highest sampling rates by comparing, in parallel, the analog input to every transition voltage, producing the output in one period with no feedback required between conversions; however, exploiting parallelism to increase speed in this manner requires the number of comparators to double the resolution of the converter in bits. Some techniques like interpolating [46] and folding [47] flash ADCs can reduce the number of preamplifiers and latches, respectively, but the general exponential growth of comparators remains a fundamental problem with this topology [48]. The widest range of applications of this type of converter is video signal processing. They are used in video tape compression, digital video transmission, radar signal analysis in particular. These applications require conversion speeds in the range of 50 MHz to 1 GHz or beyond.

The SAR ADC is generally used for medium-high resolution, medium-low frequency operation. By determining the digital output one bit at a time, SAR ADCs only make b comparisons for a b-bit converter but require at least b+1 clock periods to produce the output, much slower than the flash topology. Although SAR ADCs have also been applied to high-resolution commercial products, the requirements of trimming/calibration procedures and the use of high supply voltage to maximize the SNR increase the production cost and power consumption [49]. The resolution of a SAR ADC is typically limited by several factors: the non-linearity due to digital-to-analog converter mismatch, the comparator noise and the size of the capacitor to decrease kT/C noise. By time-interleaving SAR ADCs [50], high speed can be achieved without sacrificing the SAR's inherent low power.

In a pipeline ADC, different stages are cascaded and the number of stages to be cascaded depends on the resolution needed at the output. The pipeline ADC needs L clock periods to perform the conversion, where L is the resolution of the ADC. However, as L voltage values are simultaneously being converted, a new digital code is presented at each clock period. This digital code will be delayed in time from the sampling instant of a value proportional to the ADC resolution [51]. Most

commonly used applications of Pipeline ADCs include high quality video systems, healthcare, radio base stations, radar systems, Ethernet, cable modems, high performance digital communication system. The accuracy requirement for a pipeline ADC decreases from first stage to the last stage. The first stage must be more accurate than the later stages. The main limitations of this type of converter is the fairly complex logic, a sample-and hold circuit on every stage and the nonlinearity of the amplifiers, which must have a good match to get a linear conversion.

Flash, SAR and pipeline ADC architectures are considered as Nyquist data converters. The maximum frequency of the signal in this kind of converters is approximately half the sampling frequency. Sigma Delta ADCs are oversampled ADCs. For oversampled conversion, the maximum signal bandwidth is low compared to the sampling frequency. Thus, those converters are used for small signal bandwidth, but can achieve high resolution.

$\Sigma\Delta$  converters are based on the principle of oversampling and noise-shaping of a given input signal. Noise shaping is combined with oversampling to further improve the conversion resolution N at the same sampling speed  $f_s$  and with the same number of ADC bits n. This is accomplished by high-pass filtering the quantization noise to displace most of its power from low frequencies where the input signal spectrum is placed to higher frequencies close to  $f_s/2$ . The amount of quantization noise power still left inside the signal bandwidth depends on the exact filtering applied in terms of filter order and cut-off frequency. In  $\Sigma\Delta$  modulators, the inherent loop filter has the particularity to reject the quantization noise away from the desired band, and therefore contributes to increase the overall modulator resolution.  $\Sigma\Delta$  converters thus offer high resolution, high integration, low power conversion and low cost.

Table II.1 compares ADC architectures presented in terms of speed, resolution, size and power consumption. For a given technology, the flash ADC achieves the fastest sampling rate among various single-channel ADC architectures. However, its size and high power consumption of this architecture make it unsuitable for high bandwidth and low power consumption applications.

|             | Flash ADC | SAR ADC     | Pipeline ADC | Sigma Delta ADC |

|-------------|-----------|-------------|--------------|-----------------|

| Speed       | High      | Low-Medium  | Medium-High  | Low             |

| Resolution  | Low       | Medium-High | Medium-High  | High            |

| Size        | High      | Low         | Medium       | Medium          |

| Power cons. | High      | Medium      | High         | Low             |

Table II.1: ADC architectures comparison

SAR ADCs have a relatively low power consumption compared to other architectures. This is because no amplifiers is needed in this ADC architecture. Pipeline ADCs are well suited for wide bandwidth and medium resolution applications, but consume a lot of power. They are in fact widely used in the feedback path of BTS digital predistortion. The  $\Sigma\Delta$  architecture is an excellent candidate for DPD because of its trade-off between power consumption and high resolution. However, as  $\Sigma\Delta$  converters are typically used for small bandwidth applications like audio which requires 20 kHz bandwidth, techniques to enable wider bandwidth operation like parallelism can be used to cope with large telecommunications signal requirements.

Several approaches to achieve high speed and high resolution ADCs have been proposed in the literature. One approach is to extend the resolution of a Nyquist rate ADC such as a pipelined converter by calibrating the converter [52]. The bandwidth can then be further extended by time-interleaving pipeline converters [53]. The previous two solutions will considerably increase the power consumption of the DPD system. Another approach is to use a very high resolution converter such as a  $\Sigma\Delta$  ADC for relatively low bandwidth signals and extend the bandwidth by reducing the oversampling ratio [54].

For our application, we can take advantage of the information on the form of the signal in order to choose the ADC architecture. In the following sections, we focus on  $\Sigma\Delta$  converters architectures for our feedback DPD ADC.

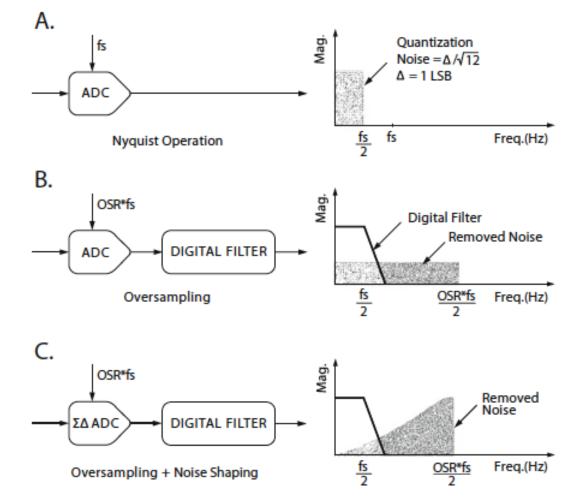

## II.2 Basics of $\Sigma\Delta$ ADCs

Sigma-Delta Analog-to-Digital Converters exploit oversampling, noise shaping, and digital signal filtering to generate a high-resolution digitized output. As presented in Section II.1.1 oversampling allows to spread the quantization noise in a wider bandwidth. Figure II.5 illustrates the three aforementionned techniques. In a typical Nyquist-rate N-bit ADC, the quantization error is considered as a noise and to be uniformly distributed within the Nyquist band of DC to  $f_s/2$ , where  $f_s$  is the sampling rate Figure II.5-A.

Applying the technique of oversampling to the same N-bit ADC, which is sampling at a higher rate by a factor of OSR, the same amount of rms quantization noise is found in the system, but the noise is now distributed over the wider bandwidth of DC to OSR  $f_s$  Figure II.5-B. By applying a digital low-pass filter (LPF) to the output, much of the quantization noise can be removed without affecting the desired signal. Therefore, a high-resolution AD conversion can be achieved by using an otherwise low-resolution ADC.

Figure II.5: Output spectra of Nyquist, oversampled and  $\Sigma\Delta$  ADCs

The main drawback of oversampling is that in order to lower the in-band quantization noise such that an N-bit increase in resolution is achieved, the system must be oversampled by a factor of  $2^2 \cdot N$ . In other words, oversampling achieves a 0.5-bit increase per doubling of OSR. This is impractical to achieve high resolutions as high-speed systems are difficult to design and lead to high power consumption. To keep the oversampling factor at a reasonable value while achieving very high resolution, the technique of noise shaping, which is shaping the quantization noise such that most of it resides outside the signal passband of interest, comes in handy. The technique is illustrated in Figure II.5-C, and is the main concept behind all  $\Sigma\Delta$  converters since it is the  $\Sigma\Delta$  modulator in such converters that allow achieving the noise-shaping characteristic.

A  $\Sigma\Delta$  ADC has three major components:

• an anti-aliasing filter which band limits the analog input signal to avoid aliasing during its subsequent sampling. As illustrated previously, oversampling

considerably relaxes the attenuation requirements of the AAF, so that smooth transition bands are usually sufficient compared to Nyquist rate ADCs.

- a ΣΔ modulator in which the oversampling and quantization of the band-limited analog signal take place. The quantization noise of the embedded B-bit quantizer is shaped in the frequency domain by placing an appropriate loop filter before it and closing a negative feedback loop around them. Low-resolution quantizers, with B typically in the range 1 to 5 bits, are sufficient for obtaining small IBN and high accuracy in the A/D conversion.

- a decimation filter in which a high-selectivity digital filter sharply removes the out-of-band spectral content of the output and thus most of the shaped quantization noise. The decimator also reduces the data rate from  $F_s$  down to the Nyquist frequency, while increasing the word length from B to N bits to preserve resolution.

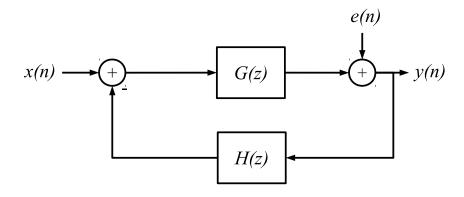

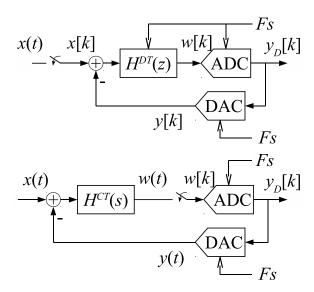

We will now focus on the basics of a  $\Sigma\Delta$  modulator as it is the block that influences the most the ADC performance. As illustrated in Figure II.6, a  $\Sigma\Delta$  modulator is made of a loop transfer function, a clocked quantizer and feedback digital-to-analog converters.

Assuming that the quantizer can be modeled with a linear additive white noise model, the modulator is modeled as the two-input (x and e) one-output (y) linear system illustrated in Figure II.6. The loop filter has two sections, a forward filter G(z) and a feedback filter H(z). The input signal X(z) is applied and compared with the signal fed back by H(z), filtered through G(z) and quantized to give the digital output. The quantization introduces an error E(z) which is modeled as input-signal-independent and directly added to the output, in the quantizer (represented as a summation point).

Figure II.6: Linear model of a  $\Sigma\Delta$  modulator

The input e is assumed to be independent of the circuit input x. The output of the modulator is then described in the Z-domain as

$$Y(z) = STF(z)X(z) + NTF(z)E(z)$$

(II.10)

where STF(z) and NTF(z) are the Signal Transfer Function and the Noise Transfer Function respectively. X(z), Y(z) and E(z) are the DT Z-domain transform of the input, output and quantization noise, respectively.

The quantization noise is shaped by the transfer function of the close loop system since the input signal is injected in a different node. Based on the feedback theory, the NTF which is in fact the transfer function for the quantization noise, is approximated as

$$NTF(z) = \frac{Y(z)}{E(z)} = \frac{1}{1 + G(z)H(z)}$$

(II.11)

where H(z) is the the loop filter function. If the loop is linearized and assuming that the gain of the quantizer and DAC is unity, by using H(z) with high passband gain, the quantization noise will be further reduced.

The transfer function for the input signal (STF) for the specific case in Figure II.6 is obtained by

$$STF(z) = \frac{Y(z)}{X(z)} = \frac{G(z)}{1 + G(z)H(z)}$$

(II.12)

The STF depends on the NTF and the topology of modulator.

Considering again the linear system of Figure II.6 and H(z) = 1. With a simple integrator

$$G(z) = \frac{1}{z - 1} \tag{II.13}$$

as the loop filter and a one-bit quantizer which produces output bits with values  $\pm 1$ . From Equation (II.10), we obtain:

$$STF(z) = z^{-1}, NTF(z) = 1 - z^{-1}$$

(II.14)

At DC (i.e., at f = 0), G(z) is infinite, which means input signals near DC should be reproduced faithfully in the output bit stream. In fact, |STF(z)| = 1 everywhere, so we at least expect the magnitude (if not the phase) of an input at any frequency to be reproduced at the output. As well, NTF(z) is close to 0 at DC, and it increases away from DC; hence, we say the quantization noise is "shaped away from DC". The simplest first-order  $\Sigma\Delta$  modulator provides a 1.5-bit increase per doubling of OSR, resulting in it being much more efficient than using only oversampling. By designing a higher order loop filter, the portion of in-band noise can be further reduced. In the case of a low pass filter, the generalized simplest expression of the NTF is given by:

$$NTF(z) = (1 - z^{-1})^{L}$$

(II.15)

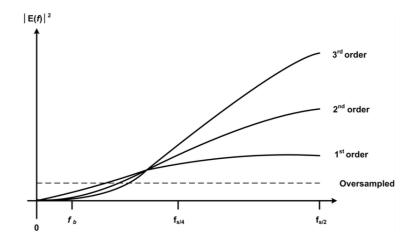

where L is the order of the loop filter. Figure II.7 illustrates the cases where L is set to 1, 2 and 3. By increasing the order of the modulator, the noise is more

Figure II.7: NTFs obtained with 1st, 2nd and 3rd order loop filters

rejected away from the low frequencies. The relation between the SNR of a Sigma Delta ADC, the loop gain, the total quantization noise power and the sampling frequency is expressed as:

$$SNR_{max} = 10\log_{10}\frac{1.5(N+1)OSR^{N+1}}{\pi^N} + 6.02(B-1)$$

(II.16)

where N is the order of the loop filter, OSR is the oversampling ratio and B is the resolution of the quantizer and feedback DACs. To achieve for example 60 dB SNR, several set of parameters can be selected. Increasing these parameters improves the resolution of the  $\Sigma\Delta$  ADC assuming the overall system is stable.

#### Out-Of-Band Gain (OOBG) and Stability

The out-of-band gain (OOBG) of a modulator is defined as the gain at the frequency  $F_s/2$ . The higher order NTF magnitudes are increasing 6 dB/order at  $F_s/2$  and need to be limited to ensure stability. High OOBG may cause overloading of the quantizer and consequently make an unusable modulator. In order to increase stability, the reduction of the loop gain is done by properly adjusting internal scaling

stage. Stability is guaranteed if the internal modulator states or equivalently the integrator outputs are bounded over time. To ensure stable operation, the input level needs to be less or equal to the full scale of the first feedback DAC. In higher-order single-bit  $\Sigma\Delta$  modulators, this input range is few dBs below the DAC full scale. This stable range is mainly determined by the NTF and the number of quantizer bits. A stability condition for single-bit modulators widely in use is the Lee's Criterion [55]:

$$|NTF_{MAX}| \le 1.5 \tag{II.17}$$

where  $NTF_{MAX}$  is the maximum magnitude over all frequencies. A NTF with the OOBG set at 1.5 suffers significantly in terms of in-band noise suppression compared to the ideal NTF. Also as the order of the modulator increases, the performance starts to saturate and the desired performance boost due to higher order filters, loses its leverage. However, the introduction of multi-bit quantization enables higher order systems to be stable even with a large OOBG.

#### II.2.1 Design Parameters

When designing a  $\Sigma\Delta$  modulator several high level parameters need to be fixed. Table II.2 gathers some of those parameters.

| Criteria                          | Classification  |  |

|-----------------------------------|-----------------|--|

| The order of the loop filter      | 1 to 5          |  |

| The NTF characteristic            | Low pass        |  |

| The NTF characteristic            | Bandpass        |  |

| The loop filter circuitry         | Discrete time   |  |

| The loop inter circuitry          | Continuous time |  |

| The number of bits in a quantizer | Single-bit      |  |

| The number of bits in a quantizer | Multi-bit       |  |

| The number of quantizers employed | Single loop     |  |

| The number of quantizers employed | Cascaded        |  |

Table II.2:  $\Sigma\Delta$  modulators classification

Each of those criteria is discussed in the following sections.

#### Oversampling ratio, modulator order and quantizer resolution

Generally, the order of H(z) (which must be strictly proper to ensure causality) is the maximum power of z in the denominator. It is possible to use a second-, third-, or even higher-order H(z) as a loop filter; generally, a converter of order

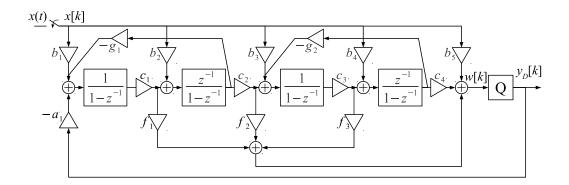

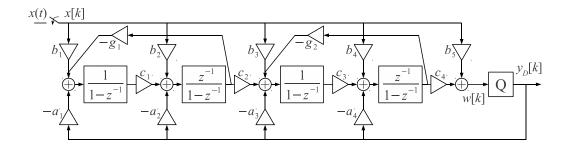

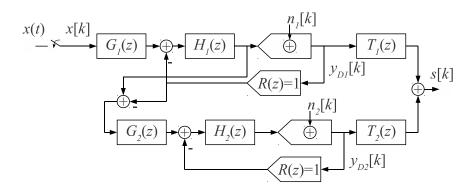

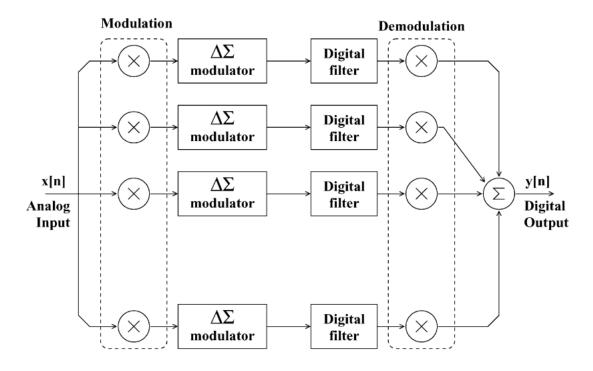

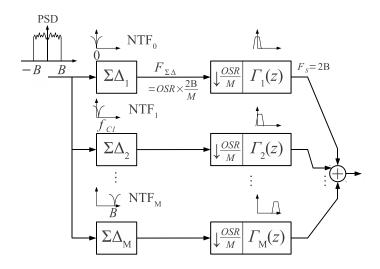

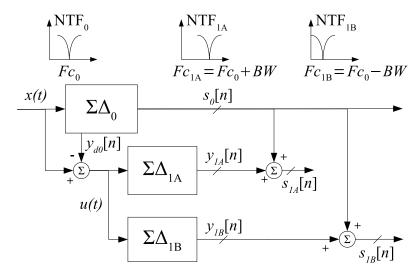

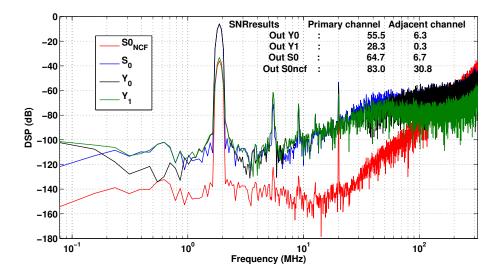

L is built as a cascade of L integrators usually surrounded with feedforward and feedback coefficients.